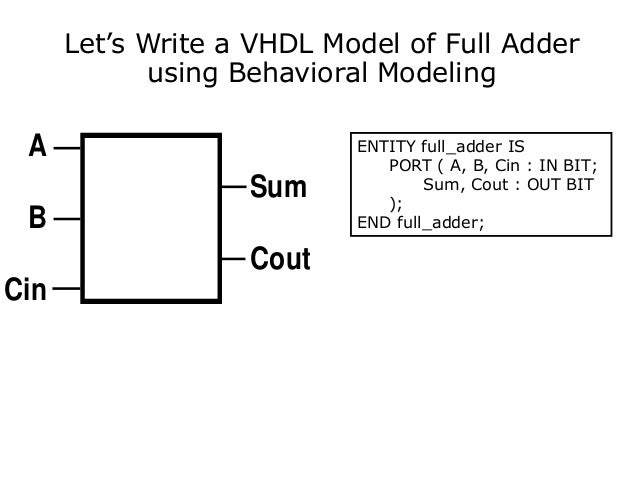

Vhdl Code For Full Adder Using Behavioral Model Vhdl Tutorial Images

Vhdl Code For Full Adder Pdf Pdf Vhdl Computing In this post, we will take a look at implementing the vhdl code for full adder using the behavioral method. first, we will explain the logic and then the syntax before writing the testbench and generating the rtl schematic and simulation waveforms. A full adder is a fundamental combinational circuit used to perform binary addition of three bits: two input bits (a, b) and a carry in (cin). the circuit produces two outputs: sum (s) and carry out (cout).

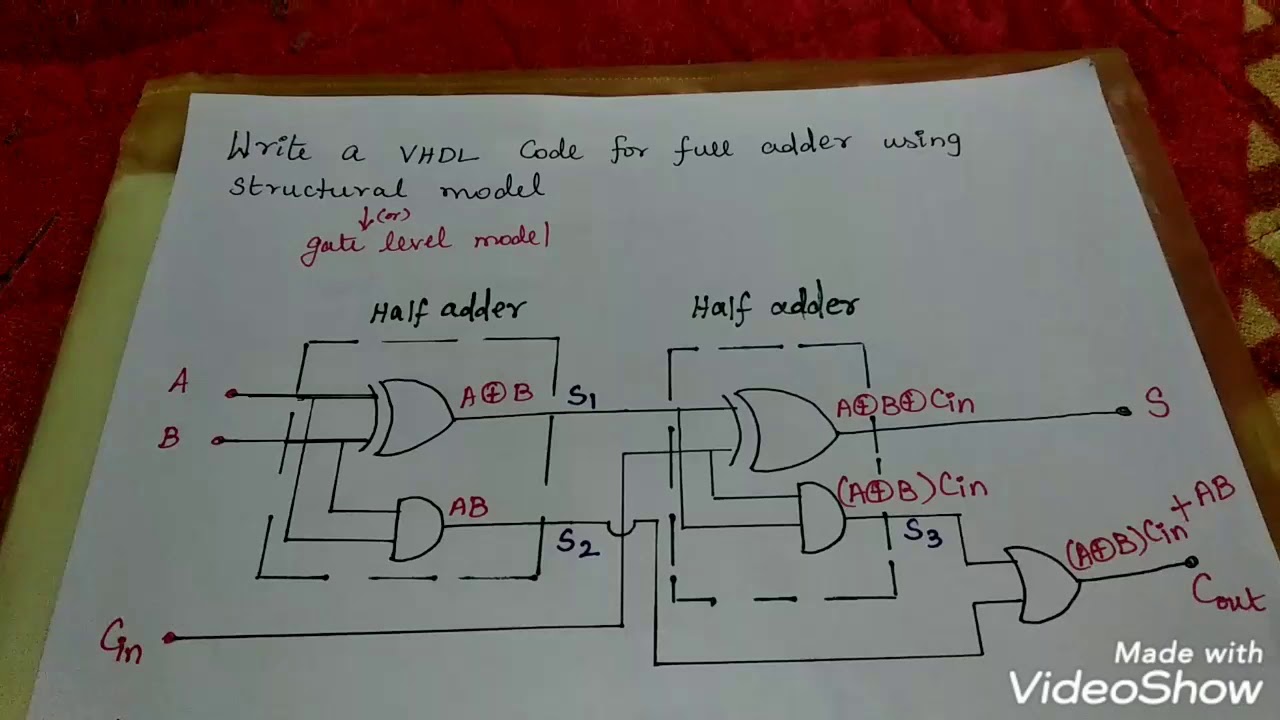

Vhdl Code For Full Adder Using Behavioral Model Vhdl Vrogue Co After watching this video, you will know about vhdl language, vhdl history, vhdl capabilities, difference between vhdlvs c language, vhdl program structure and types of modeling styles of. Vhdl code for the adder is implemented by using behavioral and structural models. the full adder has three inputs x1, x2, carry in cin and two outputs s, carry out cout as shown in the following figure: the vhdl code for the full adder using the structural model: library ieee; . use ieee.std logic 1164.all; . The vhdl code for full adder circuit adds three one bit binary numbers (a b cin) and outputs two one bit binary numbers, a sum (s) and a carry (cout). Vhdl code to design a full adder using different modeling style. a full adder is a combinational circuit that adds two one bits numbers.

Vhdl Code For Full Adder Using Behavioral Model Vhdl Vrogue Co The vhdl code for full adder circuit adds three one bit binary numbers (a b cin) and outputs two one bit binary numbers, a sum (s) and a carry (cout). Vhdl code to design a full adder using different modeling style. a full adder is a combinational circuit that adds two one bits numbers. Aim: write down vhdl program for full adder using behavioural model, structural model and data flow model. system description: full adder is a combinational circuit that performs the addition of three binary digits. This document contains vhdl code for three different models structural, dataflow, and behavioral of a full adder circuit. the structural model uses two half adder components. the dataflow model defines the output logic for the sum and carry out signals. Understanding how to implement a full adder in vhdl is essential for designing more complex arithmetic circuits and systems. in this post, i will guide you through the main components of a full adder, explain the logic behind it, and show you how to write its vhdl code step by step. 2nd year engineering savitribai phule university (pune) digital electronics and logic design syllabus.

Vhdl Code For Full Adder Using Behavioral Model Vhdl Vrogue Co Aim: write down vhdl program for full adder using behavioural model, structural model and data flow model. system description: full adder is a combinational circuit that performs the addition of three binary digits. This document contains vhdl code for three different models structural, dataflow, and behavioral of a full adder circuit. the structural model uses two half adder components. the dataflow model defines the output logic for the sum and carry out signals. Understanding how to implement a full adder in vhdl is essential for designing more complex arithmetic circuits and systems. in this post, i will guide you through the main components of a full adder, explain the logic behind it, and show you how to write its vhdl code step by step. 2nd year engineering savitribai phule university (pune) digital electronics and logic design syllabus.

Vhdl Code For Full Adder Using Behavioral Model Vhdl Tutorial Images Understanding how to implement a full adder in vhdl is essential for designing more complex arithmetic circuits and systems. in this post, i will guide you through the main components of a full adder, explain the logic behind it, and show you how to write its vhdl code step by step. 2nd year engineering savitribai phule university (pune) digital electronics and logic design syllabus.

Vhdl Code For Full Adder Using Behavioral Model Vhdl Tutorial Images

Comments are closed.