Verilog Code For 4 To 16 Decoder Using 2 To 4 Decoder Printable Online

4 To 16 Decoder Using 2 To 4 Decoder Verilog Code Pasadesign Hot Sex I'm currently working on a verilog project where i'm attempting to run a testbench for a 4x16 decoder using a 2x4 decoder. however, i'm encountering problems with the output. i've provided the code below, and i believe i've correctly connected all the ports. This 4 to 16 decoder takes one 4 bit input and outputs a 16 bit representation of the input. this module uses the concept of one hot decoding where each output would have one output that would correspond to the input.

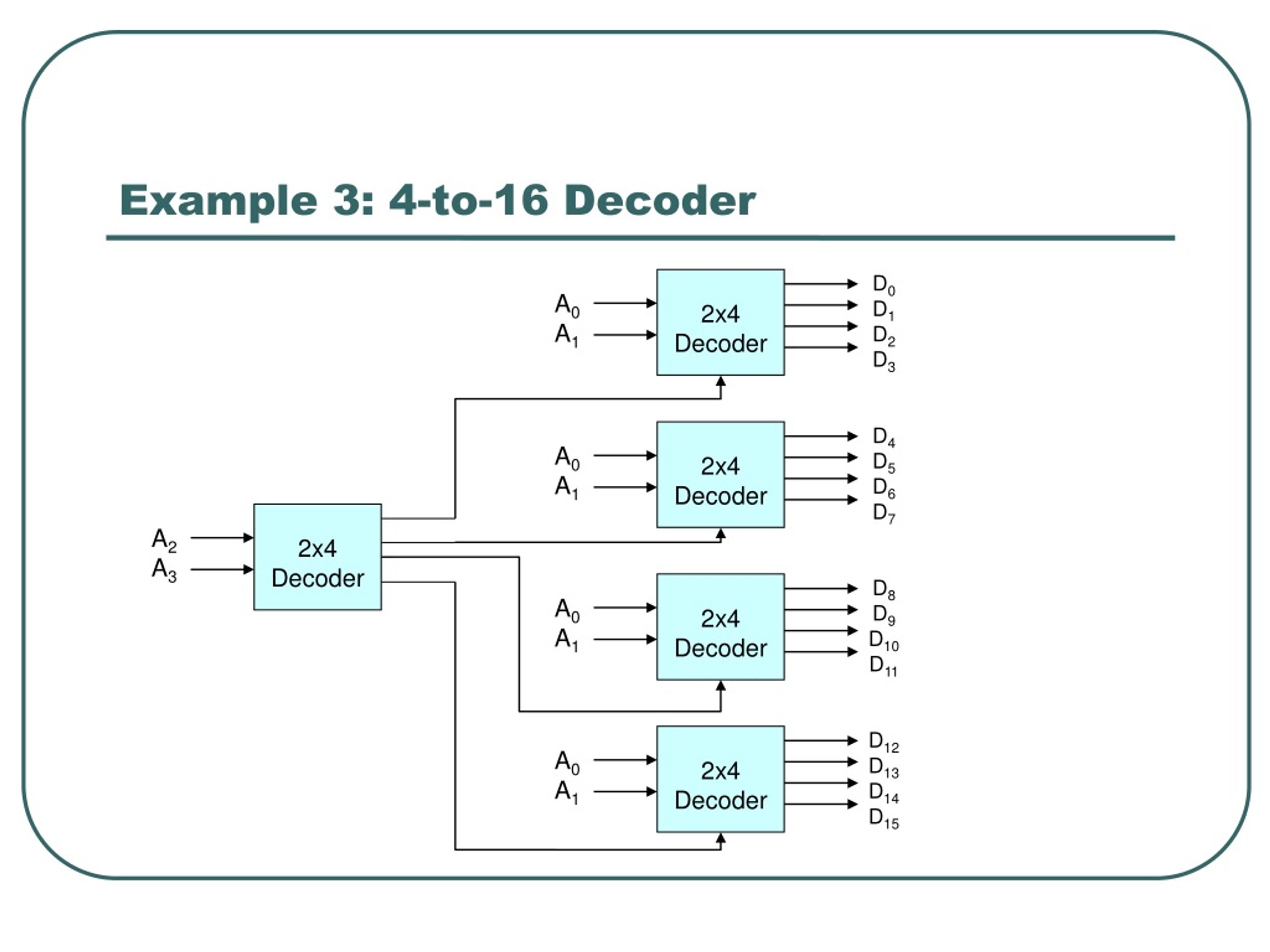

Solved Design And Write Verilog Code For A 4 To 16 Decoder Chegg Draw a circuit for a 4 to 16 decoder using only 2 to 4 decoders. copyright © 2025 circuitverse, all rights reserved. Boolean function prove using verilog (hdl) code by quartus ii. voltage divider circuit from 12v to 9v & 6v using #pspice simulation. (ভোল্টেজ ডিভাইডর). Verilog code for 4x16 decoder module decoder 4x16 (d out, d in); output [15:0] d out; input [3:0] d in; parameter tmp = 16'b0000 0000 0000 0001; assign d out = (d in == 4'b0000) ? tmp : (d in == 4'b0001) ? tmp<<1: (d in == 4'b0010) ? tmp<<2: (d in == 4'b0011) ? tmp<<3: (d in == 4'b0100) ? tmp<<4: (d in == 4'b0101) ? tmp<<5: (d in == 4'b0110. Write a verilog program for 2 to 4 decoder a decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different.

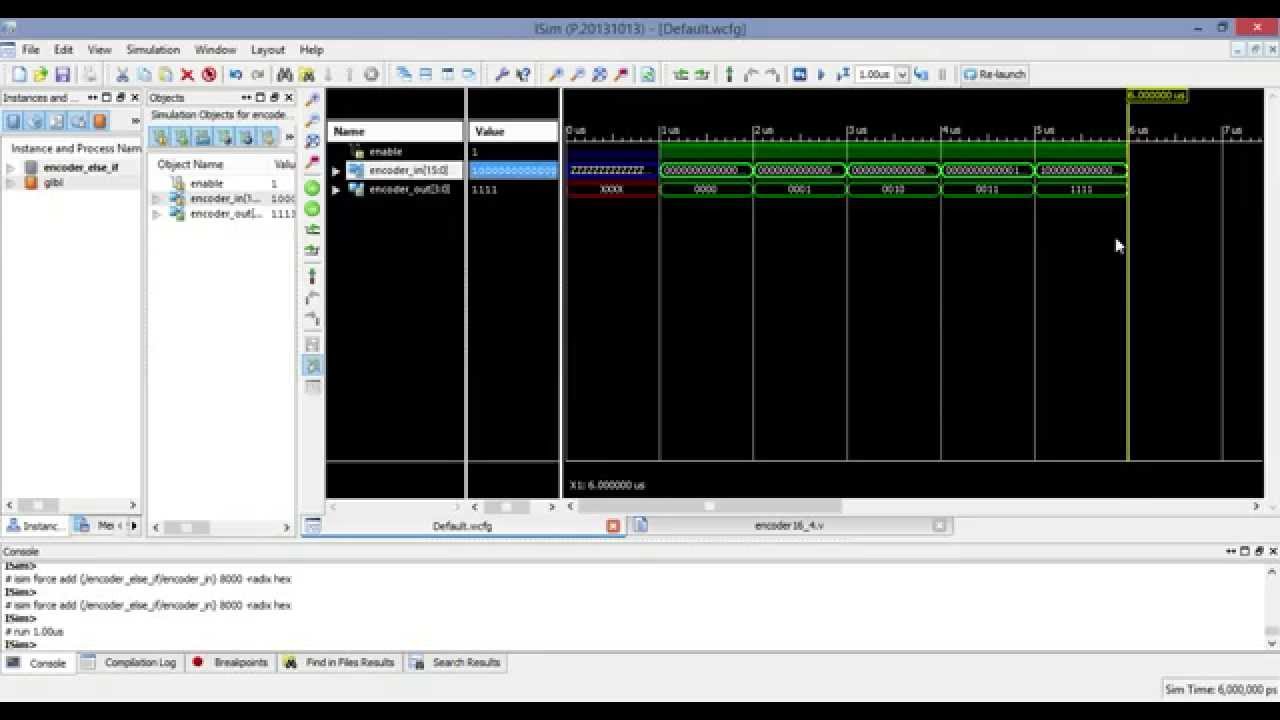

4 To 16 Decoder Using 2 To 4 Decoder Verilog Code Callswes Verilog code for 4x16 decoder module decoder 4x16 (d out, d in); output [15:0] d out; input [3:0] d in; parameter tmp = 16'b0000 0000 0000 0001; assign d out = (d in == 4'b0000) ? tmp : (d in == 4'b0001) ? tmp<<1: (d in == 4'b0010) ? tmp<<2: (d in == 4'b0011) ? tmp<<3: (d in == 4'b0100) ? tmp<<4: (d in == 4'b0101) ? tmp<<5: (d in == 4'b0110. Write a verilog program for 2 to 4 decoder a decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different. Verilog code of decoder 3 to 8 decoder verilog code 3 to 8 decoder verilog code using case statement in this post we are going to share with you the … read more. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. This repository contains the verilog implementation, layout, and analysis of a 4 to 16 decoder using the microwind tool. the project demonstrates the design, simulation, and optimization of a combinational digital circuit that decodes a 4 bit binary input into one of 16 unique output lines. I have implemented a 4x16 decoder using verilog along with it's test. for each case the decoder should output a 16 bit digit with only one of the bits high. i can't manage to get all the desired outputs when i run the program. here is the code for the decoder and test, and the output at the console: 4x16 decoder: if(enable == 1'b0).

Verilog Code For 4 To 16 Decoder Using 2 To 4 Decoder Printable Online Verilog code of decoder 3 to 8 decoder verilog code 3 to 8 decoder verilog code using case statement in this post we are going to share with you the … read more. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. This repository contains the verilog implementation, layout, and analysis of a 4 to 16 decoder using the microwind tool. the project demonstrates the design, simulation, and optimization of a combinational digital circuit that decodes a 4 bit binary input into one of 16 unique output lines. I have implemented a 4x16 decoder using verilog along with it's test. for each case the decoder should output a 16 bit digit with only one of the bits high. i can't manage to get all the desired outputs when i run the program. here is the code for the decoder and test, and the output at the console: 4x16 decoder: if(enable == 1'b0).

Comments are closed.