Ternary Logic Based Halfadder And Full Adder Pptx

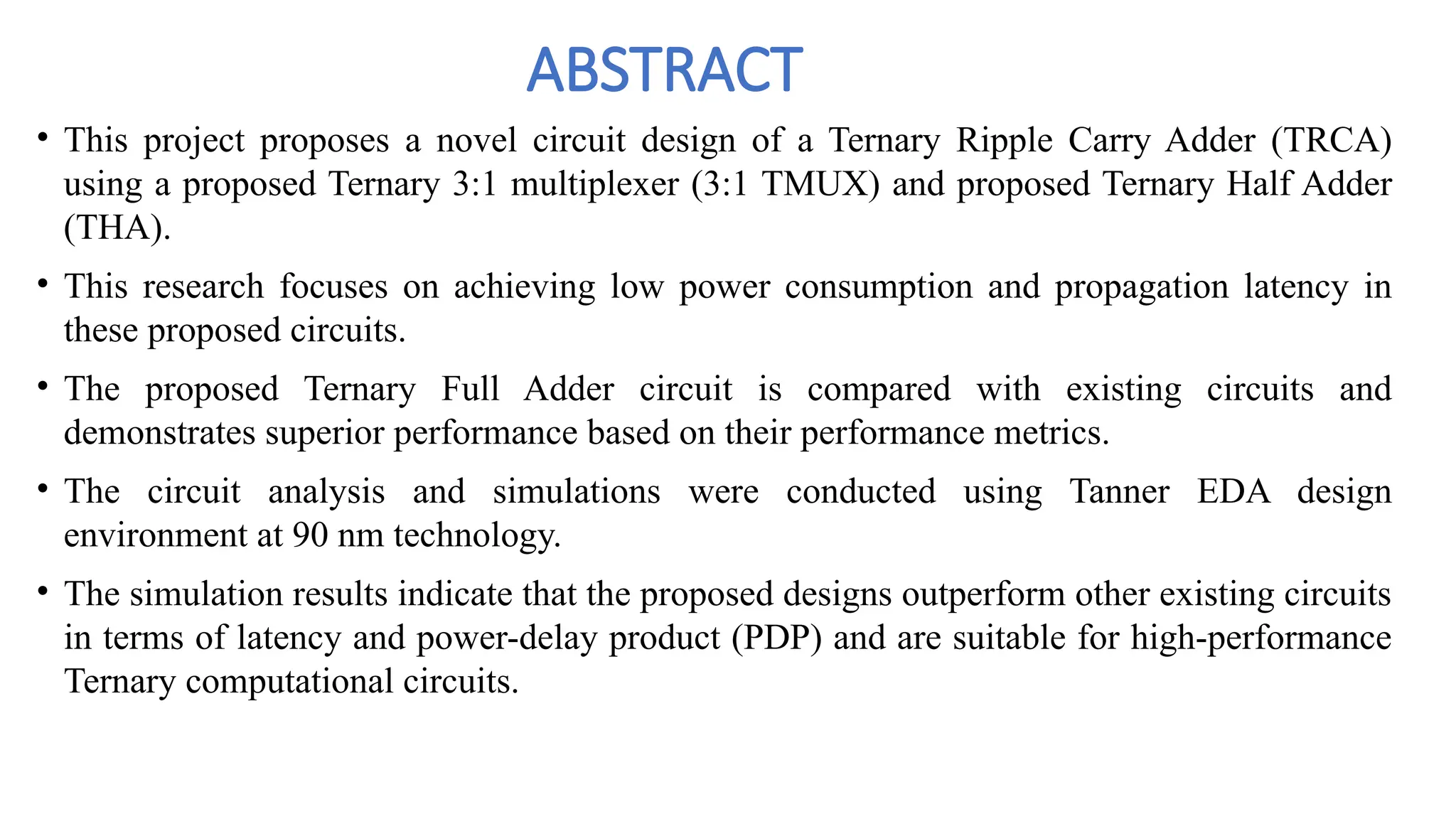

Half Adder And Full Adder Pdf The document presents a performance analysis of a ternary ripple carry adder design using a ternary 3:1 multiplexer and ternary half adder, emphasizing low power consumption and propagation latency. Outline single bit addition carry ripple adder carry skip adder carry lookahead adder carry select adder carry increment adder tree adder single bit addition half adder full adder pgk for a full adder, define what happens to carries (in terms of a and b) generate: cout = 1 independent of c g = a • b propagate: cout = c p = a b kill: cout = 0.

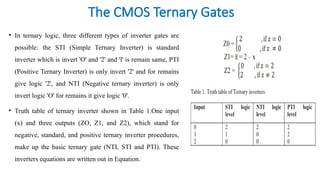

Ternary Logic Based Halfadder And Full Adder Pptx • in modern computers and other kinds of processors, adders are used in the arithmetic logic unit (alu), but also in other parts of the processor, where they are used to calculate addresses, table indices, and similar operations. The main difference between a half adder and a full adder is that the full adder has three inputs and two outputs. the first two inputs are a and b and the third input is an input carry designated as cin. We can use two half adder circuits. These equations lead to several implementations. a full adder is similar to a half adder, but includes a carry in bit from lower stages. like the half adder, it computes a sum bit, s and a carry bit, c. the carry bit c is 1 if both x and y are 1 (the sum is 2), or if the sum is 1 and a carry in (z) occurs. thus c can be re written as:.

Ternary Logic Based Halfadder And Full Adder Pptx We can use two half adder circuits. These equations lead to several implementations. a full adder is similar to a half adder, but includes a carry in bit from lower stages. like the half adder, it computes a sum bit, s and a carry bit, c. the carry bit c is 1 if both x and y are 1 (the sum is 2), or if the sum is 1 and a carry in (z) occurs. thus c can be re written as:. It is implemented using two half adders joined by an or gate. the main difference between a half adder and full adder is that a full adder has three inputs and two outputs, allowing multiple adders to be chained to add more bits. download as a ppt, pdf or view online for free. Common combinational circuits made up from individual logic gates that carryoutadesiredapplicationincludemultiplexer,de multiplexers, encoders,decoders,fullandhalfaddersetc. Full adders and half adders are usually represented by a truth table and circuit diagram in powerpoint presentations. these diagrams show the inputs and outputs of the circuits, along with the circuit design itself. The document outlines the design and construction of half adder and full adder circuits, including the necessary components, truth tables, and boolean equations.

Ternary Logic Based Halfadder And Full Adder Pptx It is implemented using two half adders joined by an or gate. the main difference between a half adder and full adder is that a full adder has three inputs and two outputs, allowing multiple adders to be chained to add more bits. download as a ppt, pdf or view online for free. Common combinational circuits made up from individual logic gates that carryoutadesiredapplicationincludemultiplexer,de multiplexers, encoders,decoders,fullandhalfaddersetc. Full adders and half adders are usually represented by a truth table and circuit diagram in powerpoint presentations. these diagrams show the inputs and outputs of the circuits, along with the circuit design itself. The document outlines the design and construction of half adder and full adder circuits, including the necessary components, truth tables, and boolean equations.

Ternary Logic Based Halfadder And Full Adder Pptx Full adders and half adders are usually represented by a truth table and circuit diagram in powerpoint presentations. these diagrams show the inputs and outputs of the circuits, along with the circuit design itself. The document outlines the design and construction of half adder and full adder circuits, including the necessary components, truth tables, and boolean equations.

Comments are closed.