Solved Problem 3 Memory Hierarchy Or A Direct Mapped Cache Chegg

Solved Problem 3 10 Points Cache Memory Suppose We Have A Chegg Your solution’s ready to go! our expert help has broken down your problem into an easy to learn solution you can count on. see answer. If someone told you the hit rate for the 3 caches is 50%, 70% and 90% but did not tell you which hit rate corresponds to which cache, which cache would you guess corresponded to which hit rate?.

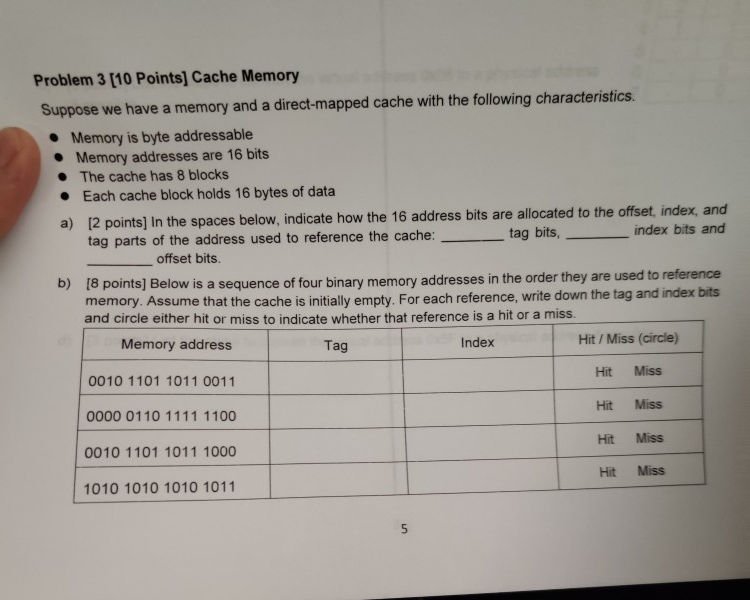

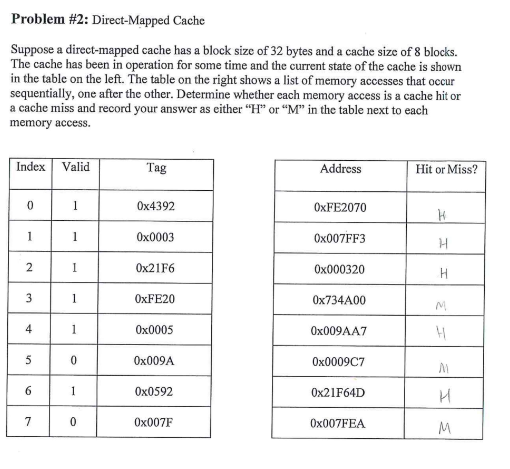

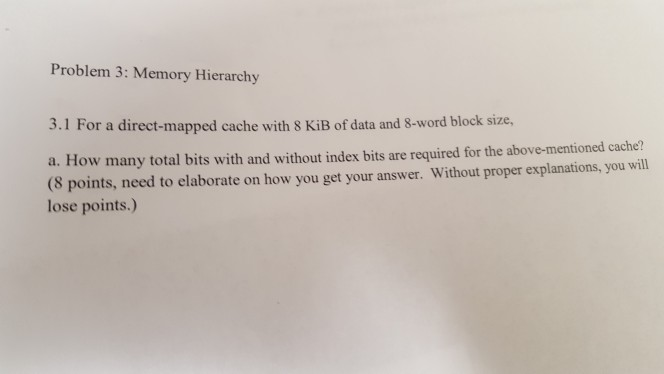

Solved Problem 2 Direct Mapped Cache Suppose A Chegg Suppose that we are designing a cache and we have a choice between a direct mapped cache where each row has a single 64 byte block of data, or a 2 way set associative cache where each row has two 32 byte blocks of data. Problem 3: (6 marks) instructions: memory hierarchy for a cache of 64k blocks, a sixteen word block size, and a 32 bit address. find the total number of sets and the total number of tag bits for caches that are: direct mapped, and eight way set associative. To solve this problem, let's first understand the concept of a direct mapped cache and how it works. 2. as a cache plays an important role to provide high performance memory hierarchy to processors. the sequence of 32 bit memory address references is given as following. Even if the cache is big and contains many stale entries, it can't simply evict those, because the position within cache is predetermined by the address. full associative cache is much more complex, and it allows to store an address into any entry.

Solved Problem 3 Memory Hierarchy Or A Direct Mapped Cache Chegg To solve this problem, let's first understand the concept of a direct mapped cache and how it works. 2. as a cache plays an important role to provide high performance memory hierarchy to processors. the sequence of 32 bit memory address references is given as following. Even if the cache is big and contains many stale entries, it can't simply evict those, because the position within cache is predetermined by the address. full associative cache is much more complex, and it allows to store an address into any entry. To have the 64kb, direct mapped cache have a lower miss rate, we want to find addresses that will map to different blocks in the larger direct mapped cache but to the same set in the 2 kb cache. Problem 4 what will be the final cache contents for a fully associative cache with one word blocks and a total size of 6 blocks? caches are important to providing a high performance memory hierarchy to processors. First assume the team chooses to build a direct mapped write back cache with a block size of 4 words. (b) this cache takes 2 clock cycles to determine if a memory access is a hit or a miss and, if it’s a hit, return data to the beta. Outline of today’s lecture ° recap of memory hierarchy & introduction to cache ° a in depth look at the operation of cache ° cache write and replacement policy.

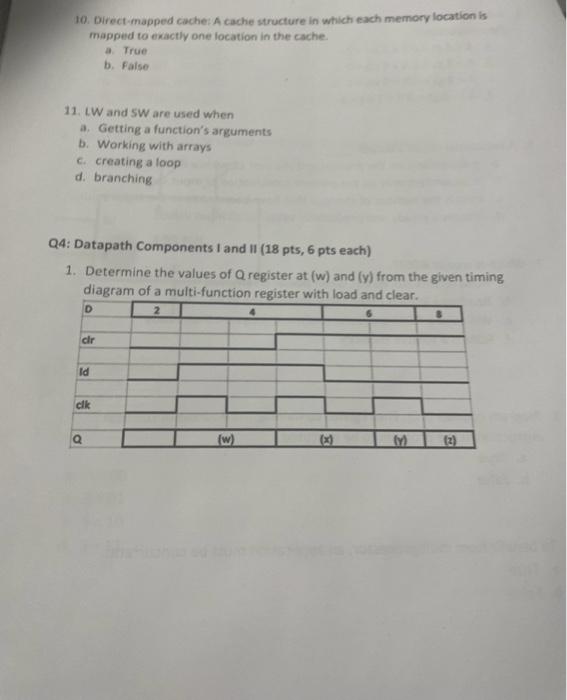

Solved 10 Direct Mapped Cache A Cache Structure In Which Chegg To have the 64kb, direct mapped cache have a lower miss rate, we want to find addresses that will map to different blocks in the larger direct mapped cache but to the same set in the 2 kb cache. Problem 4 what will be the final cache contents for a fully associative cache with one word blocks and a total size of 6 blocks? caches are important to providing a high performance memory hierarchy to processors. First assume the team chooses to build a direct mapped write back cache with a block size of 4 words. (b) this cache takes 2 clock cycles to determine if a memory access is a hit or a miss and, if it’s a hit, return data to the beta. Outline of today’s lecture ° recap of memory hierarchy & introduction to cache ° a in depth look at the operation of cache ° cache write and replacement policy.

Solved 10 Direct Mapped Cache A Cache Structure In Which Chegg First assume the team chooses to build a direct mapped write back cache with a block size of 4 words. (b) this cache takes 2 clock cycles to determine if a memory access is a hit or a miss and, if it’s a hit, return data to the beta. Outline of today’s lecture ° recap of memory hierarchy & introduction to cache ° a in depth look at the operation of cache ° cache write and replacement policy.

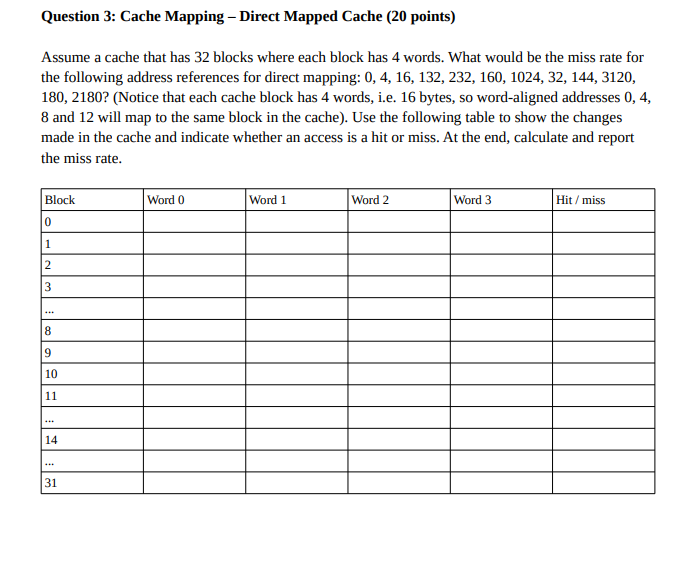

Solved Question 3 Cache Mapping Direct Mapped Cache 20 Chegg

Comments are closed.