Solved Just Want The Code And Testbench Of This Model In Chegg

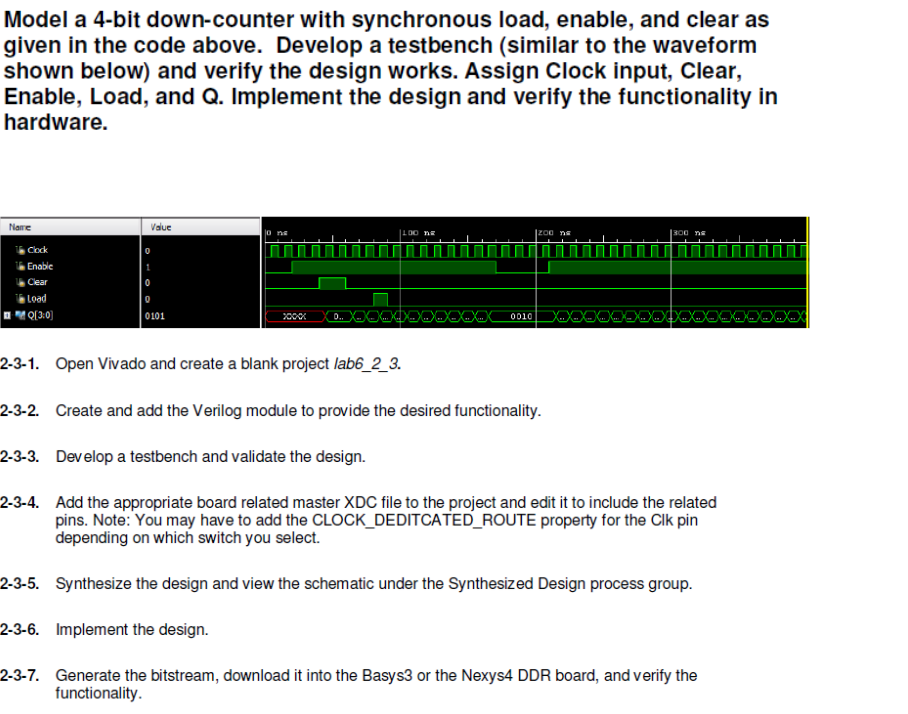

Chegg Pdf Model a 4 bit down counter with synchronous load, enable, and clear as given in the code above. develop a testbench (similar to the waveform shown below) and verify the design works. To start a testbench for the module msgchk, you will first have to declare the testbench module itself and the inputs such as clk, s, and d that the module would require.

Solved Just Want The Code And Testbench Of This Model In Chegg Also, write a testbench to test your design. you are free to use any interface, variable names, etc. for all the designs in this homework, unless explicitly stated. Create a vhdl test bench code to simulate the 2×4 | chegg . 1. create a vhdl test bench code to simulate the 2×4 decoder. use the structural model created in lab2w3 as your design source code. 2. run the testbench on your 2×4 decoder to create the waveform for your design. 3. submit the following: a. Write the code for a test bench file to run a simulation of the full adder as described in the file full adder.v (name the test bench file as full adder tb.v) and run the simulation. Step 1 here is a testbench in vhdl code for the requirements outlined in 2.4.1 2.6 of the project:.

Solved Question Chegg Write the code for a test bench file to run a simulation of the full adder as described in the file full adder.v (name the test bench file as full adder tb.v) and run the simulation. Step 1 here is a testbench in vhdl code for the requirements outlined in 2.4.1 2.6 of the project:. Our expert help has broken down your problem into an easy to learn solution you can count on. here’s the best way to solve it. I was trying to write a testbench to verify the behavior of a calculator including the error detection feature. i must verify that it detects errors, that error bit is cleared when a clear operation is performed and that other operations are blocked when the error bit is set, but it is not working. A c c test bench using xsi typically uses the following steps: open the design. fetch the ids of each top level port. set values on top level input ports. run the simulation for a specific amount of time. fetch the values of top level output ports. set values on top level input ports. run the simulation for a specific amount of time. Figure 2 54: behavioral model for code converter using a single process this is a behavioral model of the mealy state machine for bcd to excess 3 code converter based on its state table. the state change occurs on the rising edge of the clock.

Solved Model Chegg Our expert help has broken down your problem into an easy to learn solution you can count on. here’s the best way to solve it. I was trying to write a testbench to verify the behavior of a calculator including the error detection feature. i must verify that it detects errors, that error bit is cleared when a clear operation is performed and that other operations are blocked when the error bit is set, but it is not working. A c c test bench using xsi typically uses the following steps: open the design. fetch the ids of each top level port. set values on top level input ports. run the simulation for a specific amount of time. fetch the values of top level output ports. set values on top level input ports. run the simulation for a specific amount of time. Figure 2 54: behavioral model for code converter using a single process this is a behavioral model of the mealy state machine for bcd to excess 3 code converter based on its state table. the state change occurs on the rising edge of the clock.

Model 1 Chegg A c c test bench using xsi typically uses the following steps: open the design. fetch the ids of each top level port. set values on top level input ports. run the simulation for a specific amount of time. fetch the values of top level output ports. set values on top level input ports. run the simulation for a specific amount of time. Figure 2 54: behavioral model for code converter using a single process this is a behavioral model of the mealy state machine for bcd to excess 3 code converter based on its state table. the state change occurs on the rising edge of the clock.

Comments are closed.