Solved How Can I Create An Instruction Decoder Device Like Chegg

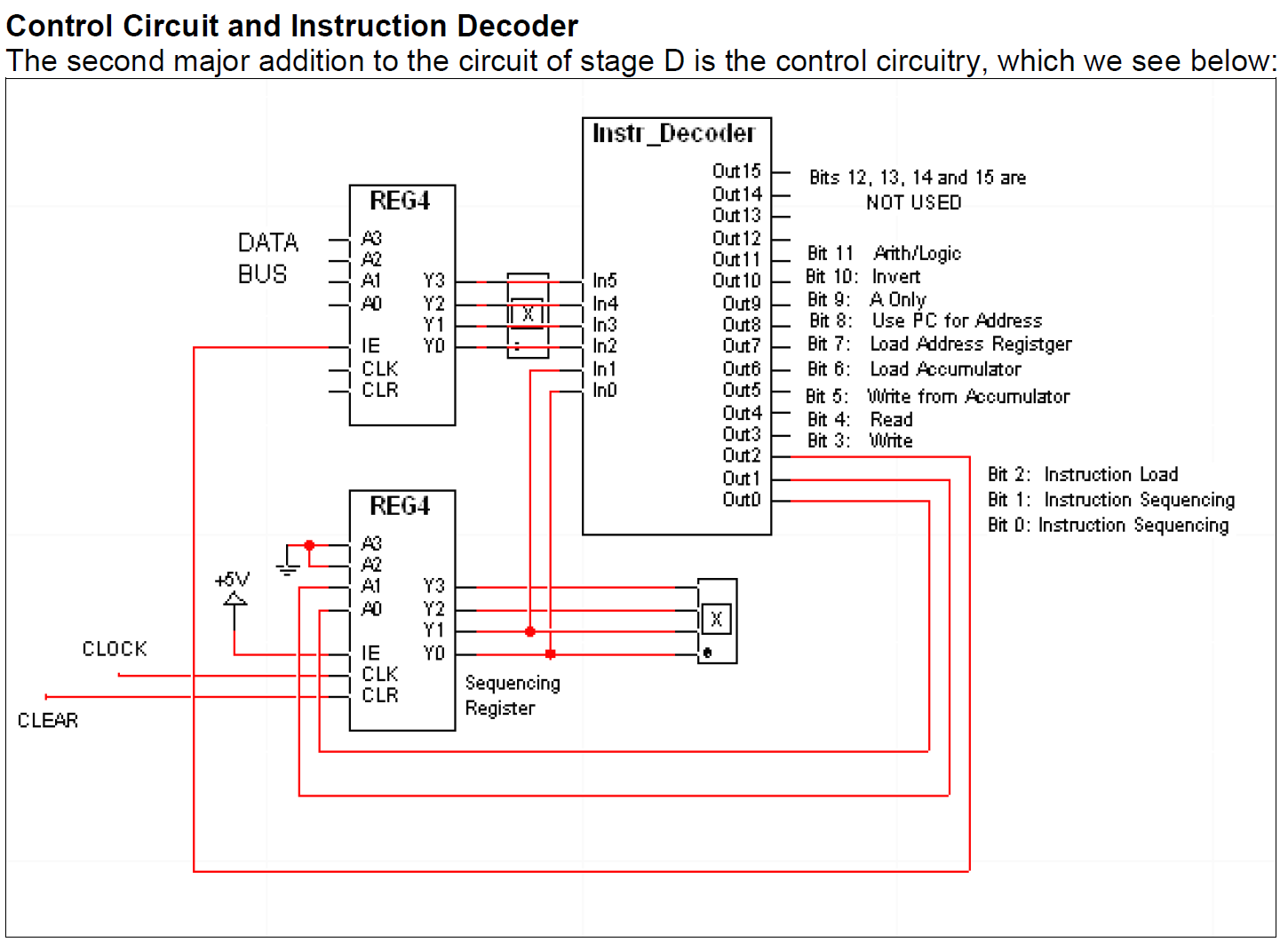

Solved How Can I Create An Instruction Decoder Device Like Chegg How can i create an instruction decoder device like the one listed below: would we simply use a 6:16 decoder? is that possible? i'm mainly concerned with how do we implement the instruction decoder device. i'm not sure if i'm supposed to be cascading multiple 2 or 4 bit decoders to get this functionality. any help is appreciated. thank you!. Answer to write verilog code to create an instruction decoder.

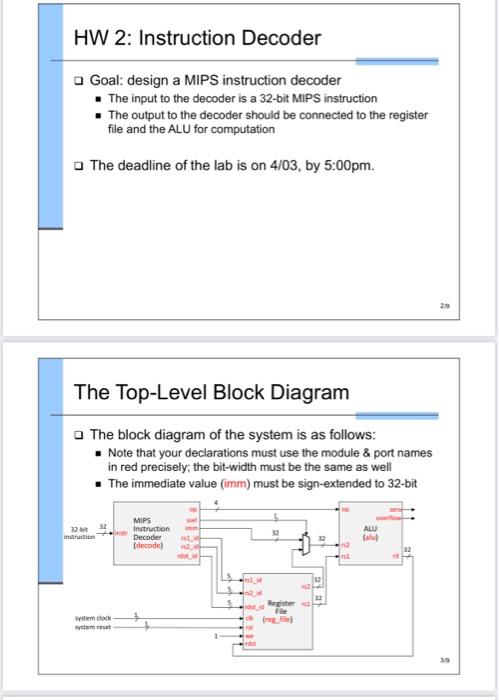

Solved Hw 2 Instruction Decoder A Goal Design A Mips Chegg The second variant includes a simple (fast) decoder between the instruction code and the hardware components. this decoding is usually implemented by discrete logic gates. Step 1 the question is asking for a decoder for the 6502 opcode, which is a way to break down the instructi. Decoder device or circuit that converts or interprets information from an encoded format. A) develop an arm7 tdmi assembly language program based instruction decoder that invoke an addition or subtraction or multiplication sub routine as per the decoding.

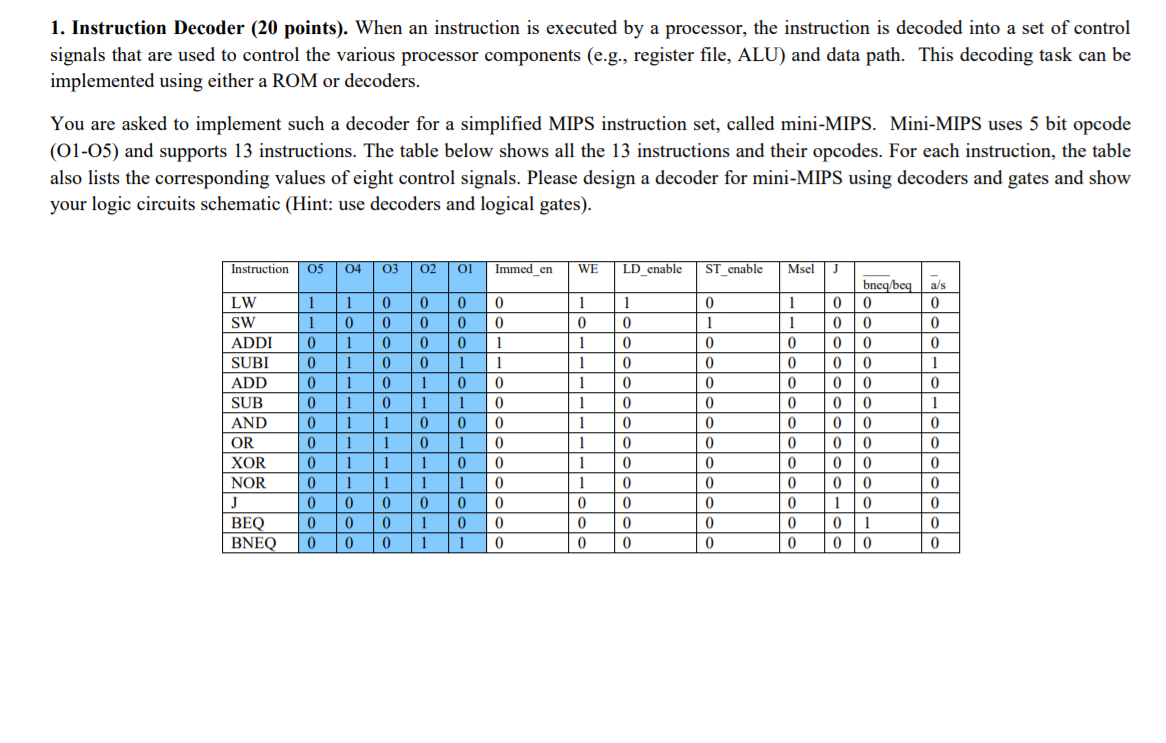

1 Instruction Decoder 20 Points When An Chegg Decoder device or circuit that converts or interprets information from an encoded format. A) develop an arm7 tdmi assembly language program based instruction decoder that invoke an addition or subtraction or multiplication sub routine as per the decoding. In an assignment to instruction set, we are told to write a sequence of instructions for arithmetic operations needed in different architecture models: accumulator, stack, load store, memory memory. Its purpose is to translate an instruction code into the address in the micro memory where the micro code for the instruction starts. in our example computer, the input to the instruction decoder is the low 5 bits of the data bus, for a total of 32 different instruction codes. Instructions supported by the isa can have instructions that are up to two words in length. due to this, the decoder will be able to account for the variable length. Although the structure for designing a decoder can be something simple if you know how to design logic circuits, the truth is that you only need to understand the process and knowing something of digital electronics so that you are designing your own decoders.

Solved The Instruction Decoder Determines The Type Of Chegg In an assignment to instruction set, we are told to write a sequence of instructions for arithmetic operations needed in different architecture models: accumulator, stack, load store, memory memory. Its purpose is to translate an instruction code into the address in the micro memory where the micro code for the instruction starts. in our example computer, the input to the instruction decoder is the low 5 bits of the data bus, for a total of 32 different instruction codes. Instructions supported by the isa can have instructions that are up to two words in length. due to this, the decoder will be able to account for the variable length. Although the structure for designing a decoder can be something simple if you know how to design logic circuits, the truth is that you only need to understand the process and knowing something of digital electronics so that you are designing your own decoders.

Comments are closed.