Solved Exercise 1 Pre Lab Design A Binary Counter Design Chegg

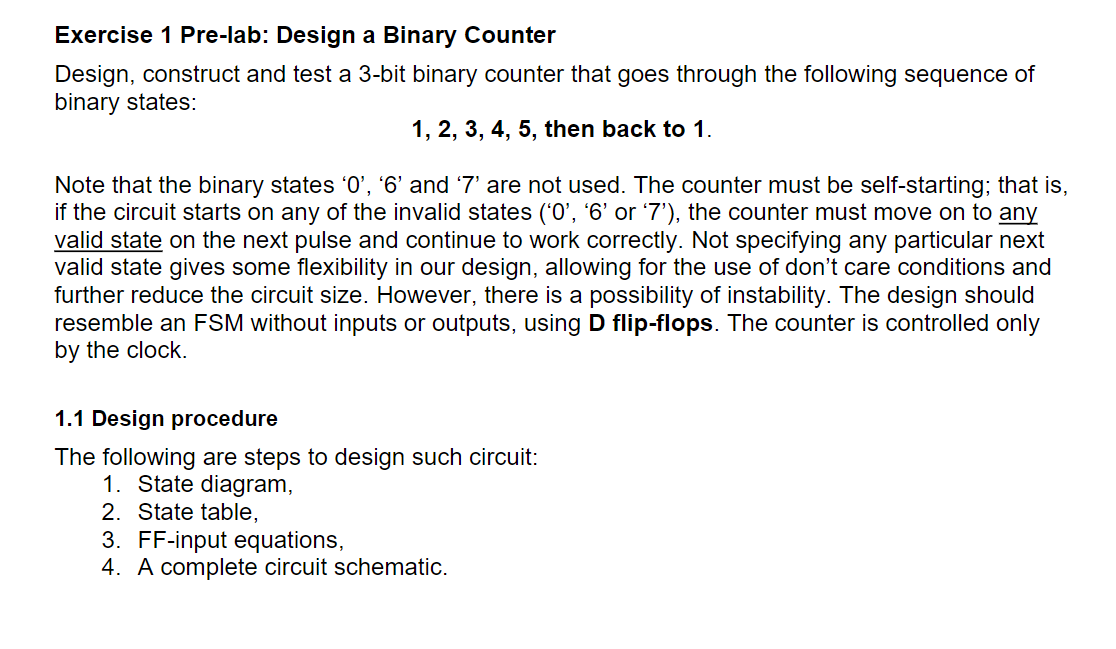

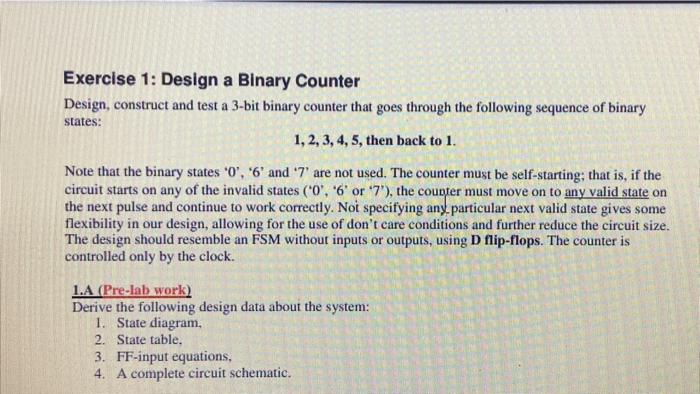

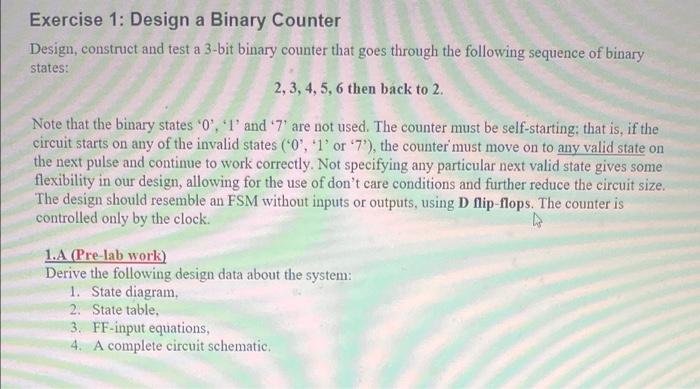

Solved Exercise 1 Pre Lab Design A Binary Counter Design Chegg Here’s the best way to solve it. exercise 1: design a binary counter design, construct and test a 3 bit binary counter that goes through the following sequence of binary states: 2,3,4,5,6 then back to 2. note that the binary states '0', 'l' and '7' are not used. Design and test a binary counter with an irregular count sequence as shown below: 001 011 100 110 001 answered step by step solved by verified expert thomas edison state college.

Solved Exercise 1 Design A Binary Counter Design Construct Chegg This is a basic outline of the design process for the 3 bit binary counter. the actual implementation may require additional components and considerations, such as clock synchronization and power supply. Today we are going to learn how abinary counterworks, and how you can use it in your lab. the 74hc393 chip contains two four bit binary counters. for now, let's just consider a single four bit counter. a four bit binary counter has four output bits q0 through q3. Question: 1. pre lab assignment the design will have two parts: • part #1 will calculate the mod 7 (x) of an arbitrary length binary input. • part #2 will generate the clock signal (cnt out) for part #1. it will be a configurable counter which is configured by a 3 bit input (configure [2:0]). Design a 4 bit binary counter. our counter has an output “q” with four bits. during correct operation, the counter starts at “0000” and then binary counts up to output “0001”, “0010”, “0011”, and so on until it outputs “1111”, after which it resets.

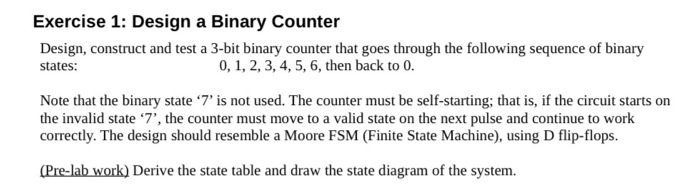

Solved Exercise 1 Design A Binary Counter Design Construct Chegg Question: 1. pre lab assignment the design will have two parts: • part #1 will calculate the mod 7 (x) of an arbitrary length binary input. • part #2 will generate the clock signal (cnt out) for part #1. it will be a configurable counter which is configured by a 3 bit input (configure [2:0]). Design a 4 bit binary counter. our counter has an output “q” with four bits. during correct operation, the counter starts at “0000” and then binary counts up to output “0001”, “0010”, “0011”, and so on until it outputs “1111”, after which it resets. Here we are going to use t flip flops, which are built using d flip flops. the t flip flops act as a toggle switch. when the input is 0, there is no change in the. output of the t flip flops. it retains the previous value. but when the input is 1, the output is. complemented. Lab 6 sequential logic circuits part 1: exercise 1 pre lab: design a binary counter exercise 2 pre lab: design a binary sequence. The part number 74hct163 integrated circuit is a high speed cmos, four bit, synchronous binary counter. it is a pre packaged unit, will all the necessary flip flops and selection logic enclosed to make your design work easier than if you had to build a counter circuit from individual flip flops. Exercise 1: design a binary counter design, construct and test a 3 bit binary counter that goes through the following sequence of binary states: 0, 1, 2, 3, 4, 5, 6, then back to 0. note that the binary state '7' is not used.

Solved Exercise 1 Design A Binary Counter Design Construct Chegg Here we are going to use t flip flops, which are built using d flip flops. the t flip flops act as a toggle switch. when the input is 0, there is no change in the. output of the t flip flops. it retains the previous value. but when the input is 1, the output is. complemented. Lab 6 sequential logic circuits part 1: exercise 1 pre lab: design a binary counter exercise 2 pre lab: design a binary sequence. The part number 74hct163 integrated circuit is a high speed cmos, four bit, synchronous binary counter. it is a pre packaged unit, will all the necessary flip flops and selection logic enclosed to make your design work easier than if you had to build a counter circuit from individual flip flops. Exercise 1: design a binary counter design, construct and test a 3 bit binary counter that goes through the following sequence of binary states: 0, 1, 2, 3, 4, 5, 6, then back to 0. note that the binary state '7' is not used.

Comments are closed.