Solved Design And Analyze A 4 Bit Binary Up Counter Learning Chegg

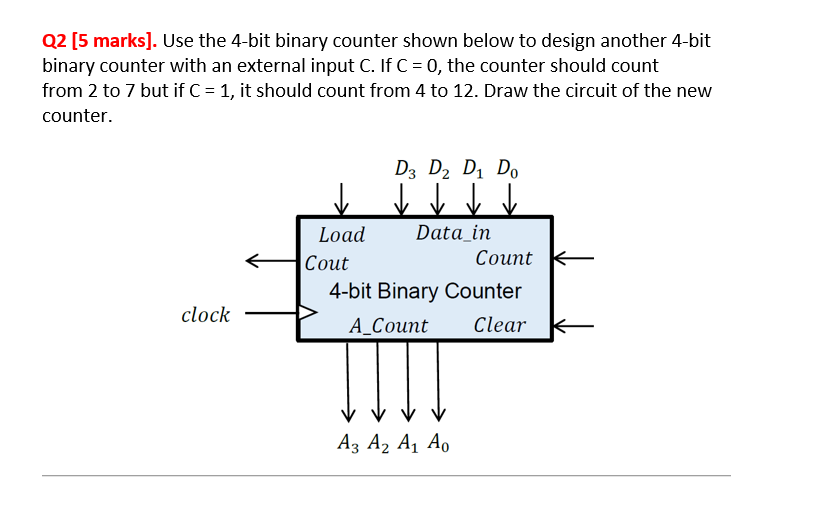

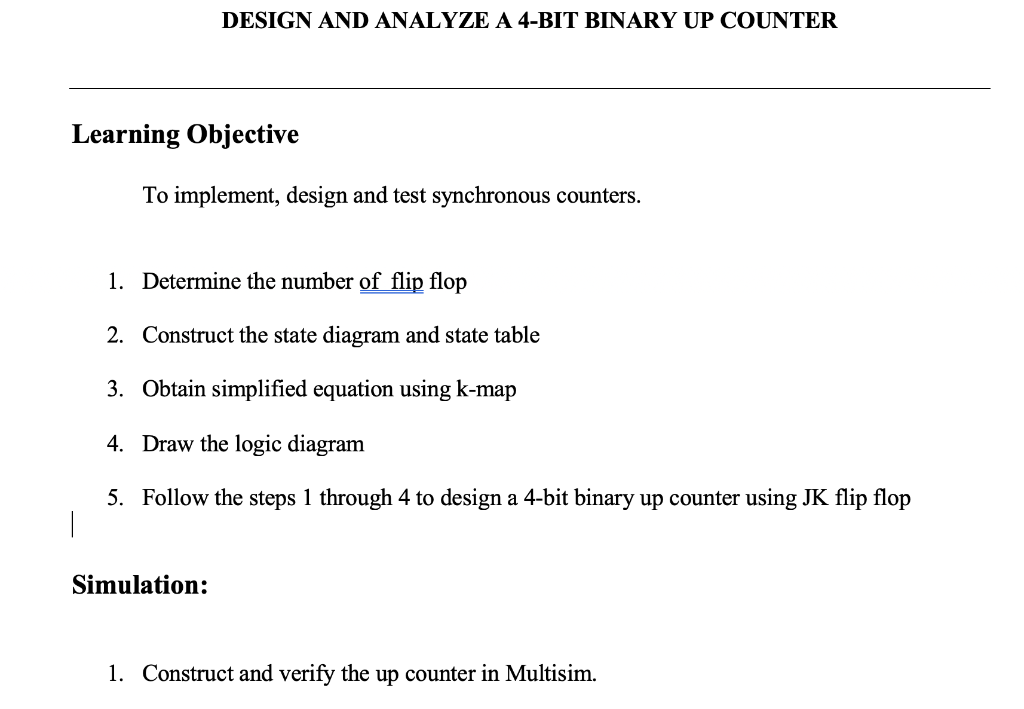

Solved Use The 4 Bit Binary Counter Shown Below To Design Chegg Design and analyze a 4 bit binary up counter learning objective to implement, design and test synchronous counters. 1. determine the number of flip flop 2. construct the state diagram and state table 3. obtain simplified equation using k map 4. draw the logic diagram 5. follow the steps 1 through 4 to design a 4 bit binary up counter using jk. Here we are going to use t flip flops, which are built using d flip flops. the t flip flops act as a toggle switch. when the input is 0, there is no change in the. output of the t flip flops. it retains the previous value. but when the input is 1, the output is. complemented.

Solved Problem 4 Design The 4 Bit Binary Up Counter With Chegg Design a circuit for an edge triggered 4 bit binary up counter (0000 to 1111). when it reaches “1111”, it should revert back to “0000” after the next edge. For this project, i chose to design a 4 bit binary counter display. this system automatically counts from 0 to 15 in binary and displays the count on a set of four leds. 1. objective n and test a 4 bit binary counter. aside from learning about the on board clock signal and push buttons as well as about frequency dividers, this lab reinforces the design flow ste ext of using the atlys fpga board. almost everything in here is applicable to the board we use now, eithe. Counter operation: this calculator simulates the behavior of a 4 bit binary up counter implemented using t flip flops. each flip flop toggles its state based on the output of the preceding flip flops.

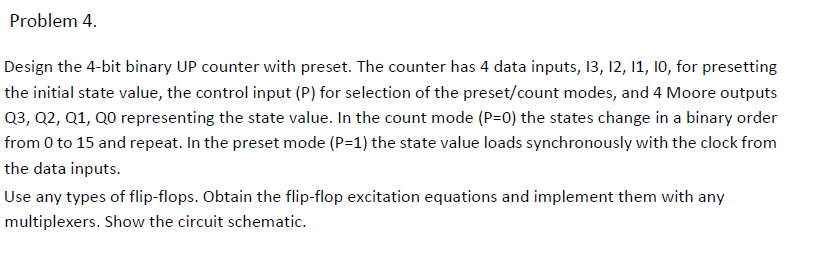

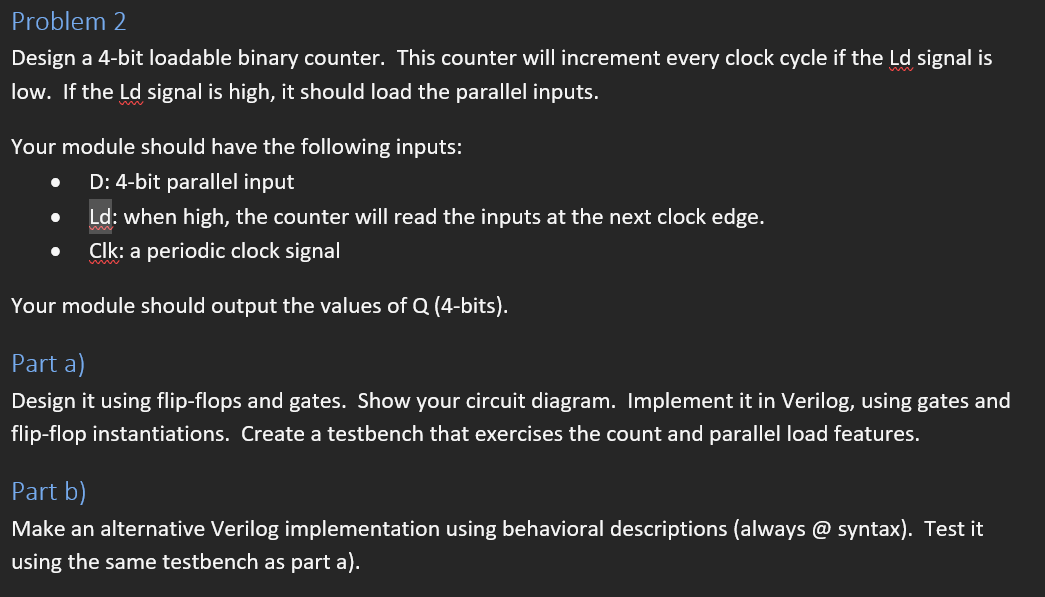

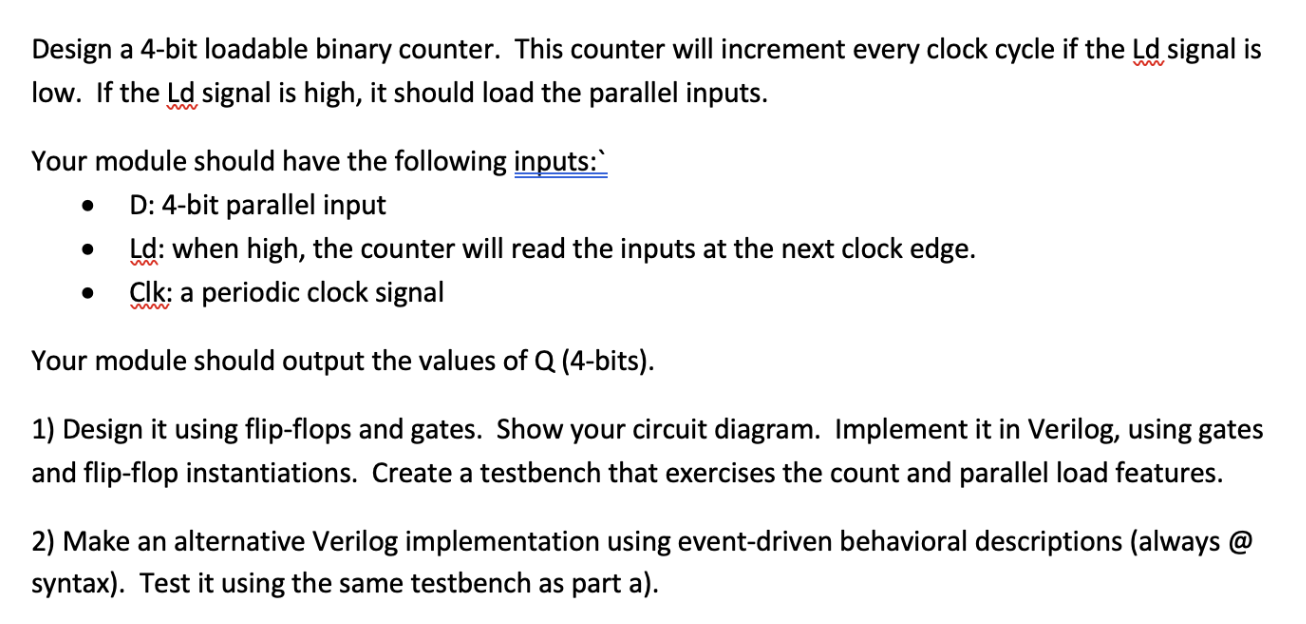

Solved Design A 4 Bit Loadable Binary Counter This Counter Chegg 1. objective n and test a 4 bit binary counter. aside from learning about the on board clock signal and push buttons as well as about frequency dividers, this lab reinforces the design flow ste ext of using the atlys fpga board. almost everything in here is applicable to the board we use now, eithe. Counter operation: this calculator simulates the behavior of a 4 bit binary up counter implemented using t flip flops. each flip flop toggles its state based on the output of the preceding flip flops. I am learning logic circuit now.i am going to design a 4 bit binary counter with d flip flop.it counts from 0 to 15.and when the number reaches 15,the number wont change and remains 15.i am now working with the add function of the circuit,but i cant find where i get wrong. There are 2 steps to solve this one. in the question it is mentioned to design a 4 bit binary up and down counter. This document presents a project on designing a 4 bit binary synchronous up counter using electric software, focusing on the creation of a jk flip flop based counter that counts from 0000 to 1111. As we are going to design a 4 bit binary up down counter which is synchronous, so all of the flipflops will have a common clock pulse. for counting up, the next flip flop will change state when there is a transition from 0 to 1. then we use the q output and connect it to the next flipflop.

Solved Design And Analyze A 4 Bit Binary Up Counter Learning Chegg I am learning logic circuit now.i am going to design a 4 bit binary counter with d flip flop.it counts from 0 to 15.and when the number reaches 15,the number wont change and remains 15.i am now working with the add function of the circuit,but i cant find where i get wrong. There are 2 steps to solve this one. in the question it is mentioned to design a 4 bit binary up and down counter. This document presents a project on designing a 4 bit binary synchronous up counter using electric software, focusing on the creation of a jk flip flop based counter that counts from 0000 to 1111. As we are going to design a 4 bit binary up down counter which is synchronous, so all of the flipflops will have a common clock pulse. for counting up, the next flip flop will change state when there is a transition from 0 to 1. then we use the q output and connect it to the next flipflop.

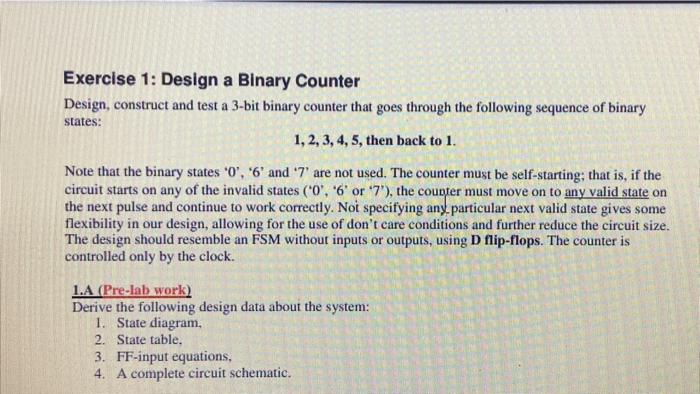

Solved Exercise 1 Design A Binary Counter Design Construct Chegg This document presents a project on designing a 4 bit binary synchronous up counter using electric software, focusing on the creation of a jk flip flop based counter that counts from 0000 to 1111. As we are going to design a 4 bit binary up down counter which is synchronous, so all of the flipflops will have a common clock pulse. for counting up, the next flip flop will change state when there is a transition from 0 to 1. then we use the q output and connect it to the next flipflop.

Design A 4 Bit Loadable Binary Counter This Counter Chegg

Comments are closed.