Soc Risc V With A Custom Vector Co Processor

Building A Risc V Processor Pdf Central Processing Unit Digital Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . Vector processors have re emerged in high performance computing and flagship mobile soc designs for their improved programmability, appealing power efficiency o.

Github Martinriis Risc V Vector Processor 256 Bit Vector Processor This paper explores the synergy between hardware and software in the context of machine learning, emphasizing the integration of dedicated vector data processors into the versatile risc v architecture. The processor bridges the gap between standard embedded control and high performance simd (single instruction, multiple data) computing, capable of processing four 16 bit words simultaneously in a single clock cycle. We give several insights into future development of embedded cnn socs, and highlight the risc v vector extension and its need for suitable auto vectorization tools, to provide easier software integration into existing dl deployment stacks. In this context, the main purpose of this proposal is to develop an asic vector engine risc v architecture compliant that implements a minimum set of the vector extension capable of the parallel processing of multiple data elements with a single instruction.

Risc V Processor Family Targets Custom Compute We give several insights into future development of embedded cnn socs, and highlight the risc v vector extension and its need for suitable auto vectorization tools, to provide easier software integration into existing dl deployment stacks. In this context, the main purpose of this proposal is to develop an asic vector engine risc v architecture compliant that implements a minimum set of the vector extension capable of the parallel processing of multiple data elements with a single instruction. To address the computational performance requirements of iot platforms when deploying convolutional neural network (cnn) models, this paper designs a scalar main processor and vector coprocessor combination architecture based on the risc v architecture. This article presents an soc capable of programmable variable precision operations on an energy efficient vector accelerator. the soc is implemented by using an agile generator based design flow that allows for rapid changes in system architecture and physical design. Its portable design allows easy integration across diverse risc v systems, making it suitable for a wide range of applications. to achieve optimal performance, this work introduces a 4 stage pipeline architecture within the vaquita co processor, specifically tailored for the risc v vector extension. This paper presents a comprehensive analysis of the risc v instruction set architecture, focusing on its modular design, implementation challenges, and performance characteristics.

Github Ishaan40 Risc V Processor A 5 Stage Pipelined Single Core To address the computational performance requirements of iot platforms when deploying convolutional neural network (cnn) models, this paper designs a scalar main processor and vector coprocessor combination architecture based on the risc v architecture. This article presents an soc capable of programmable variable precision operations on an energy efficient vector accelerator. the soc is implemented by using an agile generator based design flow that allows for rapid changes in system architecture and physical design. Its portable design allows easy integration across diverse risc v systems, making it suitable for a wide range of applications. to achieve optimal performance, this work introduces a 4 stage pipeline architecture within the vaquita co processor, specifically tailored for the risc v vector extension. This paper presents a comprehensive analysis of the risc v instruction set architecture, focusing on its modular design, implementation challenges, and performance characteristics.

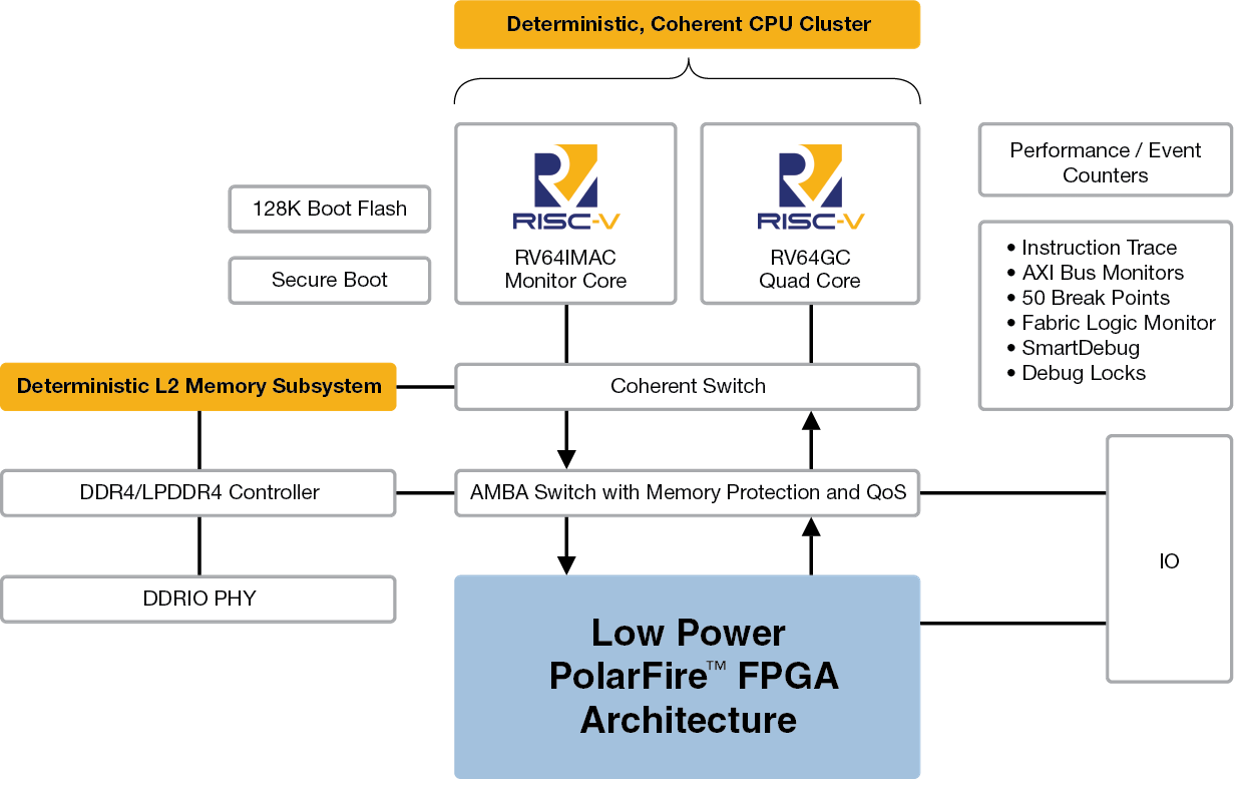

Soc Is Based On Royalty Free Risc V Instruction Set Architecture Isa Its portable design allows easy integration across diverse risc v systems, making it suitable for a wide range of applications. to achieve optimal performance, this work introduces a 4 stage pipeline architecture within the vaquita co processor, specifically tailored for the risc v vector extension. This paper presents a comprehensive analysis of the risc v instruction set architecture, focusing on its modular design, implementation challenges, and performance characteristics.

Comments are closed.