Pipelines In Mips Processors Overview

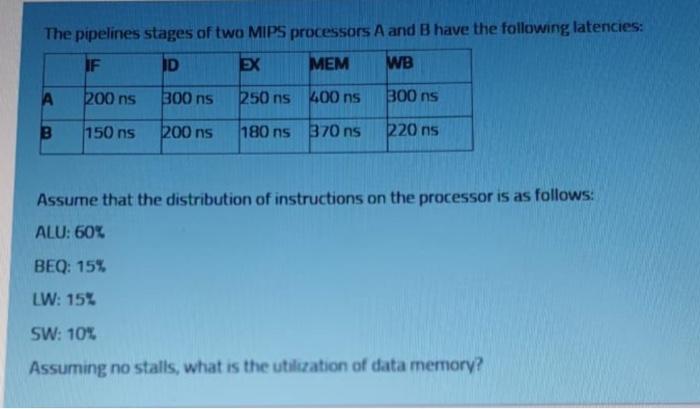

Solved The Pipelines Stages Of Two Mips Processors A And B Chegg This is an overview of pipelining in a mips processor for computer architecture classes. Pipelining: multistage pipeline which allows the cpu to perform more than one instruction at a time. the predictability (and similarity) of the time for all instructions aids in creating an efficient pipeline.

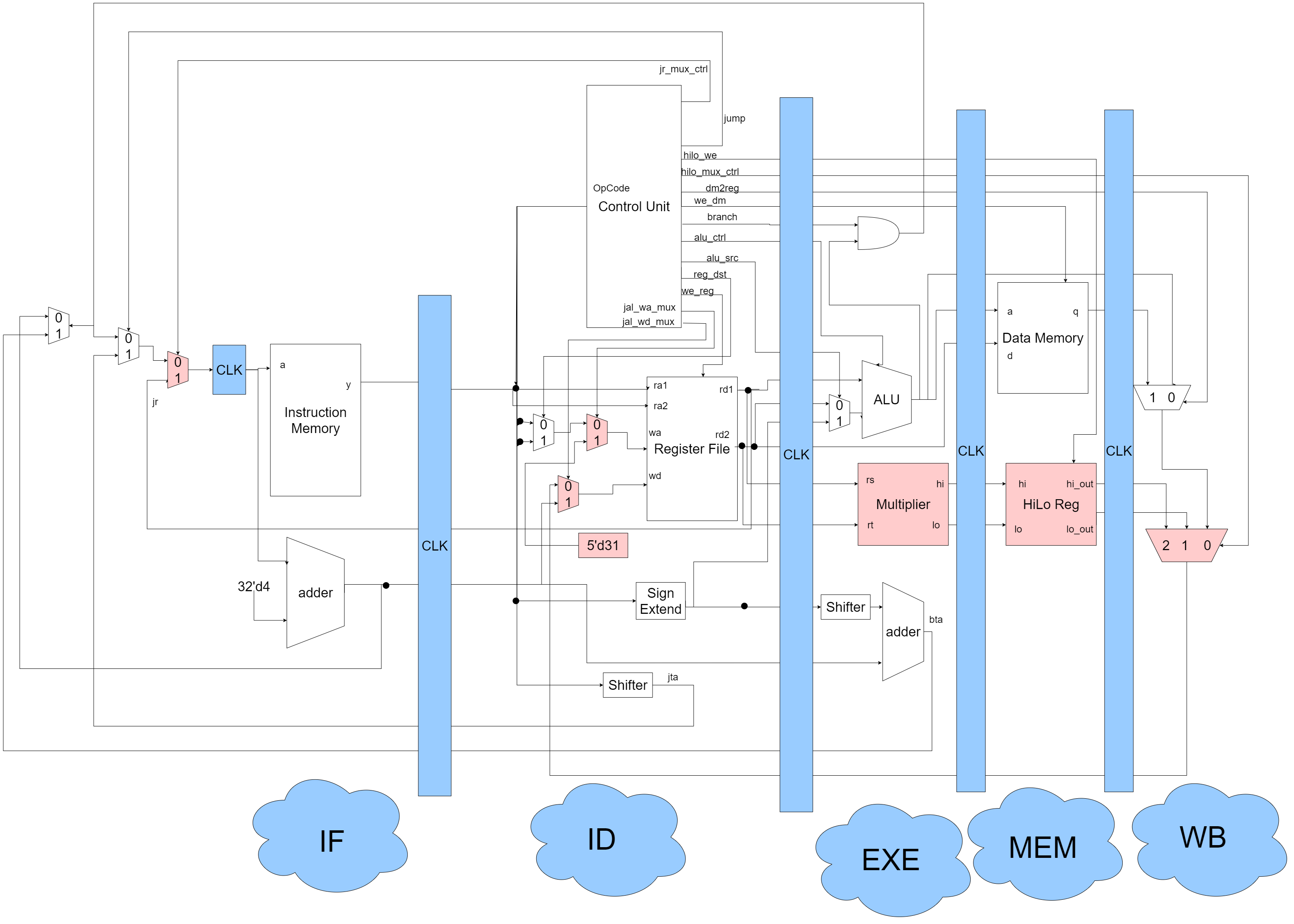

Github Lunghuiwu Mips Pipeline Processor Review: multi cycle processor advantages better mips and smaller clock period (higher clock frequency) hence, better performance than single cycle processor. Today pipelined processors has more pipelined stages than mips. you know some operations take more time than others. Table below shows same control signals grouped by pipeline stage. can’t forward backward in time! how do we detect when to forward? 1a. ex mem.registerrd = id ex.registerrs 1b. ex mem.registerrd = id ex.registerrt. 2a. mem wb.registerrd = id ex.registerrs 2b. mem wb.registerrd = id ex.registerrt. simplified pipeline w. no forwarding. One way of overcoming this problem is to go in for a pipelined implementation. we shall now discuss the basics of pipelining. pipelining is a particularly effective way of organizing parallel activity in a computer system. the basic idea is very simple.

Fpga Implemented Mips Assembly Processor Table below shows same control signals grouped by pipeline stage. can’t forward backward in time! how do we detect when to forward? 1a. ex mem.registerrd = id ex.registerrs 1b. ex mem.registerrd = id ex.registerrt. 2a. mem wb.registerrd = id ex.registerrs 2b. mem wb.registerrd = id ex.registerrt. simplified pipeline w. no forwarding. One way of overcoming this problem is to go in for a pipelined implementation. we shall now discuss the basics of pipelining. pipelining is a particularly effective way of organizing parallel activity in a computer system. the basic idea is very simple. Mips is a modular architecture supporting up to four coprocessors (cp0 1 2 3). in mips terminology, cp0 is the system control coprocessor (an essential part of the processor that is implementation defined in mips i–v), cp1 is an optional floating point unit (fpu) and cp2 3 are optional implementation defined coprocessors (mips iii removed cp3 and reused its opcodes for other purposes). for. I've tried to answer to the first question creating a pipeline diagram with the 5 stages (fetch, decode, execute, memory access, write back) and this is what i've done:. Contention for resources: what to do when two instructions need to use the same piece of hardware? how to stop their execution? solution to this problem shown a little later. not all instructions require all stages. instead of $t2? questions?. A pipelined mips processor goal to we make the processor faster! • start the next instruction before the current one has completed. divide execution time of an instruction into stages (like in multicycle) and overlap the execution of instructions such that we can perform different things on different instruction in the same clock cycle.

Github Nimaiji Mips Pipeline Cpu рџ Mips Pipeline Processor Simulator Mips is a modular architecture supporting up to four coprocessors (cp0 1 2 3). in mips terminology, cp0 is the system control coprocessor (an essential part of the processor that is implementation defined in mips i–v), cp1 is an optional floating point unit (fpu) and cp2 3 are optional implementation defined coprocessors (mips iii removed cp3 and reused its opcodes for other purposes). for. I've tried to answer to the first question creating a pipeline diagram with the 5 stages (fetch, decode, execute, memory access, write back) and this is what i've done:. Contention for resources: what to do when two instructions need to use the same piece of hardware? how to stop their execution? solution to this problem shown a little later. not all instructions require all stages. instead of $t2? questions?. A pipelined mips processor goal to we make the processor faster! • start the next instruction before the current one has completed. divide execution time of an instruction into stages (like in multicycle) and overlap the execution of instructions such that we can perform different things on different instruction in the same clock cycle.

Github Es717249 Mips Pipeline Mips With Pipeline 5 Stages Contention for resources: what to do when two instructions need to use the same piece of hardware? how to stop their execution? solution to this problem shown a little later. not all instructions require all stages. instead of $t2? questions?. A pipelined mips processor goal to we make the processor faster! • start the next instruction before the current one has completed. divide execution time of an instruction into stages (like in multicycle) and overlap the execution of instructions such that we can perform different things on different instruction in the same clock cycle.

Github Abdelrahmanabdelnabi Mips Pipelined Processor Implementation

Comments are closed.