Mod 10 Counter Design Using Schematic Deep Dive To Digital

Solved Using The Following Schematic Mod 10 Counter As A Chegg In this video, we will design and simulate a mod 10 counter (0–9) on a seven segment display (ssd) using verilog hdl. this project is very useful for beginners in digital design and fpga. Whether you’re building a frequency counter or digital clock, the mod 10 ripple counter circuit diagram is the perfect solution for getting accurate and reliable results. it’s easy to construct and requires minimal setup, making it the ideal choice for digital counting projects.

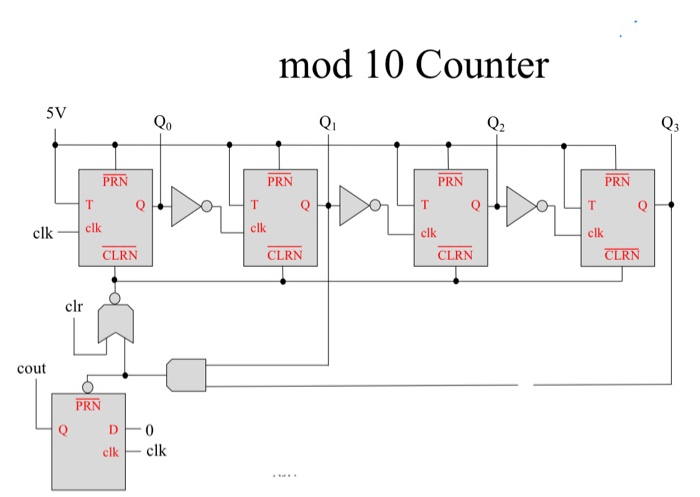

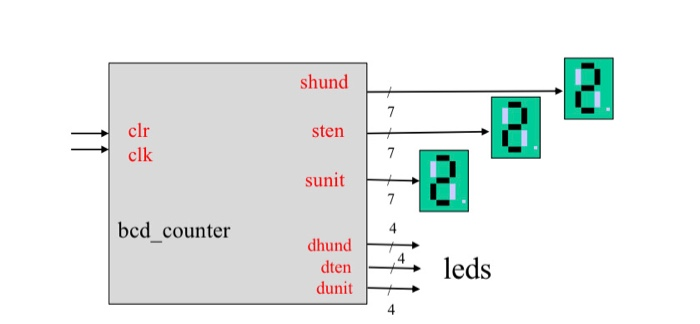

Solved Using The Following Schematic Mod 10 Counter As A Chegg This repository offers an open source solution for designing and verifying a mod 10 loadable up down counter, typically used in digital systems for counting applications. To design the combinational circuit of valid states, following truth table and k map is drawn: from the above truth table, we draw the k maps and get the expression for the mod 10 asynchronous counter. This combination of a mod 10 up asynchronous counter and a seven segment display is commonly used in digital electronics for applications such as digital clocks, timers, and other devices where a visual representation of numeric values is required. The vhdl code of the mod 10 counter is going to be something new. to break it down, the code consists of three statements: the process (lines 5 23), and the two csas (concurrent signal assignments) on lines 24 and 25.

B ï Mod 10 ï Up Down Counterdesign And Implement A Chegg This combination of a mod 10 up asynchronous counter and a seven segment display is commonly used in digital electronics for applications such as digital clocks, timers, and other devices where a visual representation of numeric values is required. The vhdl code of the mod 10 counter is going to be something new. to break it down, the code consists of three statements: the process (lines 5 23), and the two csas (concurrent signal assignments) on lines 24 and 25. Learn the intricate details of designing an asynchronous mod 10 counter, unraveling its functionalities and applications. join us for a comprehensive breakdown, simplifying complex concepts. The document details the design and implementation of counters for a digital clock using the dsch program, which allows for hierarchical logic design and simulation. This can be achieved using additional logic gates to detect the count of 9 and generate a reset signal. output: the q outputs of the four flip flops represent the mod 10 counter's current count in binary coded decimal (bcd) format. This repository contains the verilog code for a loadable mod 10 up down counter. the counter supports counting up or down from 0 to 9 (mod 10) and has a loadable feature to set a specific start value.

Design Mod 10 Asynchronous Counter Learn the intricate details of designing an asynchronous mod 10 counter, unraveling its functionalities and applications. join us for a comprehensive breakdown, simplifying complex concepts. The document details the design and implementation of counters for a digital clock using the dsch program, which allows for hierarchical logic design and simulation. This can be achieved using additional logic gates to detect the count of 9 and generate a reset signal. output: the q outputs of the four flip flops represent the mod 10 counter's current count in binary coded decimal (bcd) format. This repository contains the verilog code for a loadable mod 10 up down counter. the counter supports counting up or down from 0 to 9 (mod 10) and has a loadable feature to set a specific start value.

Design Mod 10 Asynchronous Counter This can be achieved using additional logic gates to detect the count of 9 and generate a reset signal. output: the q outputs of the four flip flops represent the mod 10 counter's current count in binary coded decimal (bcd) format. This repository contains the verilog code for a loadable mod 10 up down counter. the counter supports counting up or down from 0 to 9 (mod 10) and has a loadable feature to set a specific start value.

Github Shravyasamala Mod10 Counter Design And Verification Mod10

Comments are closed.