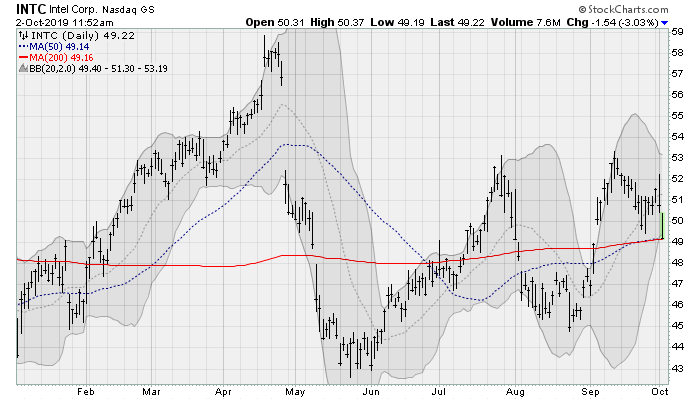

Intc Amd Nvda Intc Has Some Dramatic Upside When They Release Their

Intc Amd Nvda Intc Has Some Dramatic Upside When They Release Their 3 np.intc is defined as an integer with the size of int in c in the compiler used to build the runtime (see here). in most modern compilers, even in 64 bit toolchains, int is defined to be 32 bits (see here). How do i convert a string to an integer in c#?.

Nvidia Stock Nvda Vs Amd Stock Amd One May Have A 121 Upside Currently im porting the vendor's uboot2022.10 for spacemit k1 soc on bananapi bpif3 lpi3a to the mainline version, and encounter some problems. i've add the driver definition in defconfig. I have a data frame that stores store name and daily sales count. i am trying to insert this to salesforce using the python script below. however, i get the following error: typeerror: object of ty. I'm trying to use microblaze interrupt to handle with simple gpio button interrupt. in the block, only gpio and uart is used as well as interrupt controller. interrupt controller is set for level. I am working with a zynq board , z turn, and i added two interruptions coming from pl, i edited my device tree with : amba pl { #address cells = <0x1>; #size cells = <0x1&.

Why Intel Intc Amd Amd And Nvidia Nvda Gained Today Thestreet I'm trying to use microblaze interrupt to handle with simple gpio button interrupt. in the block, only gpio and uart is used as well as interrupt controller. interrupt controller is set for level. I am working with a zynq board , z turn, and i added two interruptions coming from pl, i edited my device tree with : amba pl { #address cells = <0x1>; #size cells = <0x1&. A pci device can potentially use up to 4 interrupt pins inta#, intb#, intc# and intd#. these signals will be wired to the interrupt controller. they are level sensitive and may be shared by other pci devices. if it has a single pci function it will typically use inta# if it uses one at all. if it has multiple pci functions, the different pci functions (up to 8) may use different interrupt pins. Xscugic softwareintr(&intcinstance, intc device int id, xscugic spi cpu1 mask); sleep(1); add a delay or triggering condition here as necessary to prevent continuous triggering } return xst success; } set start addr() and release acpus() are verified to work properly. the main function runs on core0 while the function core1 runs on core1. I have a simple microblaze setup with two gpio (push button and switches). i want to handle both devices interrupts. here follows my current non working code. #include<xparameters.h> #inclu. 2 intc 3 3 3 amd 2 2 5 amd2 1 0 7 armh 5 0 9 aapl 7 0 when i run the following command, i keep the smallest inttime but the rows are not conserved.

Intc Stock Intel Still Has Sizable Upside Potential Investorplace A pci device can potentially use up to 4 interrupt pins inta#, intb#, intc# and intd#. these signals will be wired to the interrupt controller. they are level sensitive and may be shared by other pci devices. if it has a single pci function it will typically use inta# if it uses one at all. if it has multiple pci functions, the different pci functions (up to 8) may use different interrupt pins. Xscugic softwareintr(&intcinstance, intc device int id, xscugic spi cpu1 mask); sleep(1); add a delay or triggering condition here as necessary to prevent continuous triggering } return xst success; } set start addr() and release acpus() are verified to work properly. the main function runs on core0 while the function core1 runs on core1. I have a simple microblaze setup with two gpio (push button and switches). i want to handle both devices interrupts. here follows my current non working code. #include<xparameters.h> #inclu. 2 intc 3 3 3 amd 2 2 5 amd2 1 0 7 armh 5 0 9 aapl 7 0 when i run the following command, i keep the smallest inttime but the rows are not conserved.

Comments are closed.