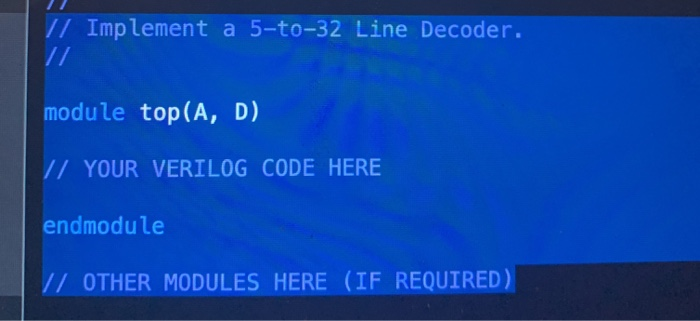

Implementing A 5 To 32 Line Decoder In Verilog

Verilog Decoder In this video, we will work through the entire process of designing and implementing a 5 to 32 line decoder in verilog. we'll start with the design on paper, implement each module. Contribute to mariamarotti verilog development by creating an account on github.

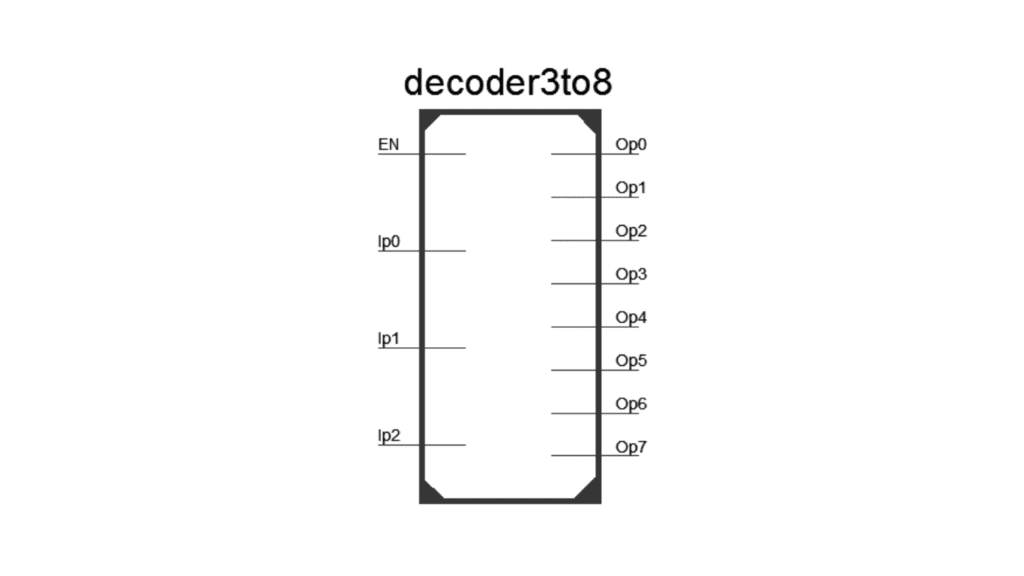

Solved Implement A 5 To 32 Line Decoder In Verilog Using Chegg So today’s topic is designing a 5:32 decoder using 4 3:8 decoders and a 2:4 decoder. many a times, it happens that we don’t have a larger decoder, so we normally combine small decoders to design a bigger one. let’s start with the theory behind it. The next example is for a 3:8 decoder that has the same valid input combinations: 000, 001, 100, 110 but in this example when the input does not have a valid value: the eight main outputs must be all zeros a new invalid output signal is set high. Here’s the best way to solve it. start by defining the module and declaring the input and output ports, specifying that a is a 5 bit input and d is a 32 bit output. Solution for implement a 5 to 32 line decoder in verilog using visual studio code using starter.v file module top (a, d); input [4:0] a; output [31:0] d; assign d = 32'b0; always @* b.

Solved Implement A 5 To 32 Line Decoder Module Top A D Chegg Here’s the best way to solve it. start by defining the module and declaring the input and output ports, specifying that a is a 5 bit input and d is a 32 bit output. Solution for implement a 5 to 32 line decoder in verilog using visual studio code using starter.v file module top (a, d); input [4:0] a; output [31:0] d; assign d = 32'b0; always @* b. Q. 4.25: construct a 5 to 32 line decoder with four 3 to 8 line decoders with enable and a 2 to 4 line decoder. use block diagrams for the components. pleas. On the day 008 of my rtl challenge, i designed 5:32 decoder using verilog hdl. it is a combinational circuit having 5 input lines and 32 output lines i.e. decoder is having the n number. Here’s the best way to solve it. module decoder using case ( binary in , 5 bit binary input decoder out , 32 bit out enable enable for the decoder ); declare input output input [4:0] binary in ; input enable ; output reg [31:0] decoder out ; always enabal or bnary inpu …. A communication transmission line has a source impedance of 85Ω and needs to be connected to a signal strength indicator meter with an impedance of 60Ω, which has a maximum display of 12db.

3 To 8 Decoder Verilog Code Siliconvlsi Q. 4.25: construct a 5 to 32 line decoder with four 3 to 8 line decoders with enable and a 2 to 4 line decoder. use block diagrams for the components. pleas. On the day 008 of my rtl challenge, i designed 5:32 decoder using verilog hdl. it is a combinational circuit having 5 input lines and 32 output lines i.e. decoder is having the n number. Here’s the best way to solve it. module decoder using case ( binary in , 5 bit binary input decoder out , 32 bit out enable enable for the decoder ); declare input output input [4:0] binary in ; input enable ; output reg [31:0] decoder out ; always enabal or bnary inpu …. A communication transmission line has a source impedance of 85Ω and needs to be connected to a signal strength indicator meter with an impedance of 60Ω, which has a maximum display of 12db.

Decoder Using Verilog The Tech Social Here’s the best way to solve it. module decoder using case ( binary in , 5 bit binary input decoder out , 32 bit out enable enable for the decoder ); declare input output input [4:0] binary in ; input enable ; output reg [31:0] decoder out ; always enabal or bnary inpu …. A communication transmission line has a source impedance of 85Ω and needs to be connected to a signal strength indicator meter with an impedance of 60Ω, which has a maximum display of 12db.

Decoder Using Verilog The Tech Social

Comments are closed.