Github Oxmose Risc V Simplist And Non Optimized Implementation Of A

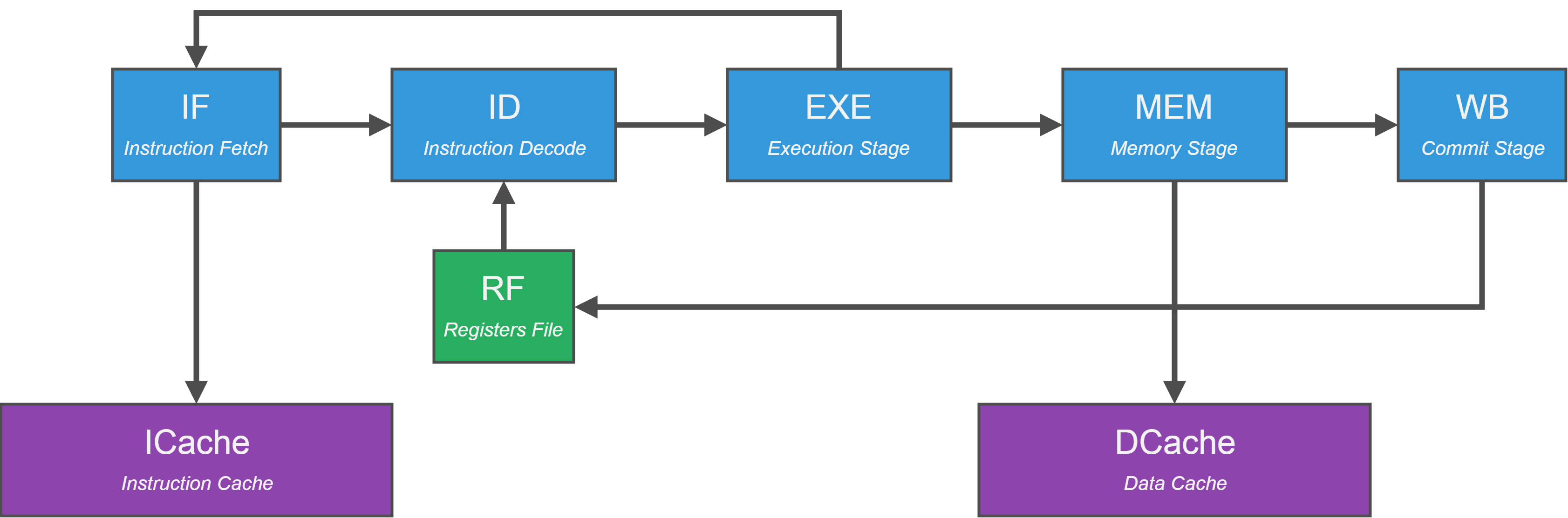

Github Oxmose Risc V Simplist And Non Optimized Implementation Of A Simple and non optimized implementation of a risc v processor. this risc v pipeline is based on the dlx architecture. implementation: risc v32i. Oxmose has 21 repositories available. follow their code on github.

Simplist Github Simplist and non optimized implementation of a risc v processor. issues · oxmose risc v. Version 6.4 of the linux kernel introduces a new syscall, riscv hwprobe that can be used to determine interesting pieces of information about the underlying risc v cpus on which a user space program runs. Checkout the starfive visionfive 8gb risc v sbc. starfive visionfive hardware specs. cpu: u74 dual core with 2mb l2 cache, running at 1.0ghz. the soc includes vision dsp tensilica vp6 for computing vision at 600mhz (vpu), an nvidia deep learning accelerator, and a neural network engine. memory: 8gb lpddr4 ram (2x 4gb clocked at 2800mhz) user i o. Let’s create a simple os that handles basic file operations and task scheduling. we’ll break this down into steps: 1. boot sequence. 2. basic kernel implementation. 3. simple task scheduler.

Oxmose Alexy Torres Github Checkout the starfive visionfive 8gb risc v sbc. starfive visionfive hardware specs. cpu: u74 dual core with 2mb l2 cache, running at 1.0ghz. the soc includes vision dsp tensilica vp6 for computing vision at 600mhz (vpu), an nvidia deep learning accelerator, and a neural network engine. memory: 8gb lpddr4 ram (2x 4gb clocked at 2800mhz) user i o. Let’s create a simple os that handles basic file operations and task scheduling. we’ll break this down into steps: 1. boot sequence. 2. basic kernel implementation. 3. simple task scheduler. Unlike most other isa designs, the risc v isa is provided under open source licenses that do not require fees to use. a number of companies are offering or have announced risc v hardware, open source operating systems with risc v support are available and the instruction set is supported in several popular software toolchains. A simple but didactic risc v processor denoted as astirv32i. the paper discusses the design strategies, memory mapping, physical verification proce ures, and perfor mance evaluation of the astirv32i processor. furthermore, it highlights the successful validation of the implemented design through the execution of fundamental algorithms. It is still my opinion that risc v could be much better designed; though i will also say that if i was building a 32 or 64 bit cpu today i'd likely implement the architecture to benefit from the existing tooling. Originally designed for computer architecture research at berkeley, risc v is now used in everything from $0.10 ch32v003 microcontroller chips to the pan european supercomputing initiative, with 64 core 2 ghz workstations in between.

Github Muhammadamarkazi Risc V Fpga Implementation Unlike most other isa designs, the risc v isa is provided under open source licenses that do not require fees to use. a number of companies are offering or have announced risc v hardware, open source operating systems with risc v support are available and the instruction set is supported in several popular software toolchains. A simple but didactic risc v processor denoted as astirv32i. the paper discusses the design strategies, memory mapping, physical verification proce ures, and perfor mance evaluation of the astirv32i processor. furthermore, it highlights the successful validation of the implemented design through the execution of fundamental algorithms. It is still my opinion that risc v could be much better designed; though i will also say that if i was building a 32 or 64 bit cpu today i'd likely implement the architecture to benefit from the existing tooling. Originally designed for computer architecture research at berkeley, risc v is now used in everything from $0.10 ch32v003 microcontroller chips to the pan european supercomputing initiative, with 64 core 2 ghz workstations in between.

Github Mohamedhussein27 Risc V Single Cycle Implementation This It is still my opinion that risc v could be much better designed; though i will also say that if i was building a 32 or 64 bit cpu today i'd likely implement the architecture to benefit from the existing tooling. Originally designed for computer architecture research at berkeley, risc v is now used in everything from $0.10 ch32v003 microcontroller chips to the pan european supercomputing initiative, with 64 core 2 ghz workstations in between.

Github Erfanmola Simplist

Comments are closed.