Get Answer Problem 7 Adder Consider The Following Building Block

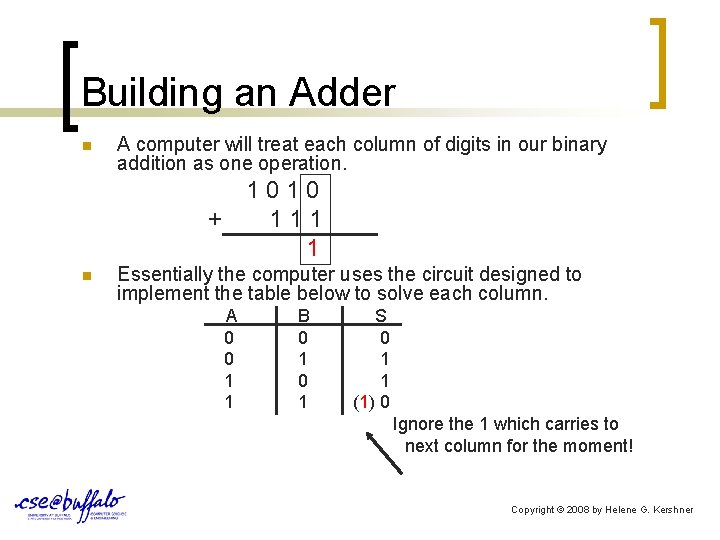

Building An Computer Adder Building An Adder N Your solution’s ready to go! our expert help has broken down your problem into an easy to learn solution you can count on. see answer question: chapter 5. problem 7: (10 pts) consider the following circuit with an active high output decoder. Problem 7 (adder) consider the following building block for a full adder. a b cout 1 bit full adder s cin a) design the corresponding circuits for the single bit full adder (draw the logic gates) and write down the functions for the sum and carry outputs. show more….

Building An Computer Adder Building An Adder N Electrical engineering document from arizona state university, 7 pages, chapter 5, problem 7: (10 pts) consider the following circuit with an active high output decoder. Use (2) 4 bit adders to build an 8 bit adder to add x=x[7:0] and y= y[7:0] and produce a sum, s[7:0], and a carry out, c8. label the inputs and outputs and make appropriate connections. The half adder is a basic building block for adding two numbers (two inputs) and produce out (two outputs). we can understand more about the function of a half adder with the block diagram, logical circuit, and truth table of a half adder as shown below:. Consider an n–bit adder. the high order sum bit is sn–1, produced in 2 (n – 1) 3 gate delays. in general, a ripple–carry adder produces a valid n–bit sum after 2 n 1 gate delays. a 32–bit sum requires 65 gate delays, about 65 to 130 nanoseconds. much too slow!.

Building An Computer Adder Building An Adder N The half adder is a basic building block for adding two numbers (two inputs) and produce out (two outputs). we can understand more about the function of a half adder with the block diagram, logical circuit, and truth table of a half adder as shown below:. Consider an n–bit adder. the high order sum bit is sn–1, produced in 2 (n – 1) 3 gate delays. in general, a ripple–carry adder produces a valid n–bit sum after 2 n 1 gate delays. a 32–bit sum requires 65 gate delays, about 65 to 130 nanoseconds. much too slow!. There is no enable input required. (for example, if xyz = 011, then output 3 would be 1 and all other outputs would be 0.) the only building block is a two input, four output decoder (with an active high enable). In computer architecture, an adder circuit is an essential component that performs arithmetic operations, such as addition and subtraction, on binary numbers. the following steps illustrate the process of creating a simple adder circuit:. In this problem you will construct a 16 bit carry look ahead adder (cla), step by step. you will then consider the implications of extending this concept to 64 bits. Chapter 5, problem 14: the following circuit includes a multiplexer with select inputs a and b, and data inputs w, x, y, and z. write an algebraic equation for f.

Comments are closed.