Fpga Dsp Fir Filter Ip With Dds Compiler In Vivado

Fpga Dsp Fir Filter With Dds Compiler In Vivado Hackster Io Generate three signals with dds compiler, and implement lowpass filter in vivado. the lowpass filter will filter the faster signal. the video is divided in. See how to integrate your custom fir with xilinx dsp ip such as their dds compiler ip.

Fpga Dsp Fir Filter With Dds Compiler In Vivado Hackster Io The finite impulse response (fir) filter is one of the most ubiquitous and fundamental building blocks in dsp systems. Table 1 2 shows the classes of filters that are supported for the fir compiler core. the supported filter configurations are described in separate sections within this document. in conjunction with table 1 1 and table 1 2, it is important to note some further limitations inherent in the core. This hands on course covers four essential xilinx dsp ip cores: fir compiler, cic compiler, dds compiler, and fast fourier transform (fft). you’ll learn how to configure and simulate each core using vivado 2024.2, generate verilog testbenches, and analyze the outputs using python. This hands on course covers four essential xilinx dsp ip cores: fir compiler, cic compiler, dds compiler, and fast fourier transform (fft). you’ll learn how to configure and simulate each core using vivado 2024.2, generate verilog testbenches, and analyze the outputs using python. we’ll explore multiple configurations for each ip core:.

Dsp For Fpga Custom Axi4 Stream Fir Filter Ip In Vivado Knitronics This hands on course covers four essential xilinx dsp ip cores: fir compiler, cic compiler, dds compiler, and fast fourier transform (fft). you’ll learn how to configure and simulate each core using vivado 2024.2, generate verilog testbenches, and analyze the outputs using python. This hands on course covers four essential xilinx dsp ip cores: fir compiler, cic compiler, dds compiler, and fast fourier transform (fft). you’ll learn how to configure and simulate each core using vivado 2024.2, generate verilog testbenches, and analyze the outputs using python. we’ll explore multiple configurations for each ip core:. This article will continue to introduce the design of fir filters using the fir ip core provided by xilinx in the vivado development environment on the basis of the first three articles. I'm currently trying to implement a simple low pass filter using the fir compiler available in the ip catalog. my design is very basic, i've generated a sine wave using the dds ip : * configuration options : phase generator and sin cos lut. * system clock : 100 mhz. * mode of operation : standard. * output frequency : 1.2 mhz. Dsp for fpga: using xilinx dds with custom fir. whitney knitter. april 1, 2021. I've closely followed the guide for implementing a custom fir filter in vivado. however, my simulation doesn't start as expected due to inout ports in the auto generated wrapper, which contrasts with the guide's direct use of reg types for clock and reset.

Interfacing Vivado Fir Compiler 7 1 Q A Fpga Reference Designs This article will continue to introduce the design of fir filters using the fir ip core provided by xilinx in the vivado development environment on the basis of the first three articles. I'm currently trying to implement a simple low pass filter using the fir compiler available in the ip catalog. my design is very basic, i've generated a sine wave using the dds ip : * configuration options : phase generator and sin cos lut. * system clock : 100 mhz. * mode of operation : standard. * output frequency : 1.2 mhz. Dsp for fpga: using xilinx dds with custom fir. whitney knitter. april 1, 2021. I've closely followed the guide for implementing a custom fir filter in vivado. however, my simulation doesn't start as expected due to inout ports in the auto generated wrapper, which contrasts with the guide's direct use of reg types for clock and reset.

Free Video Xilinx Hls Fpga Fir Filter Design In C In 30 Minutes From Dsp for fpga: using xilinx dds with custom fir. whitney knitter. april 1, 2021. I've closely followed the guide for implementing a custom fir filter in vivado. however, my simulation doesn't start as expected due to inout ports in the auto generated wrapper, which contrasts with the guide's direct use of reg types for clock and reset.

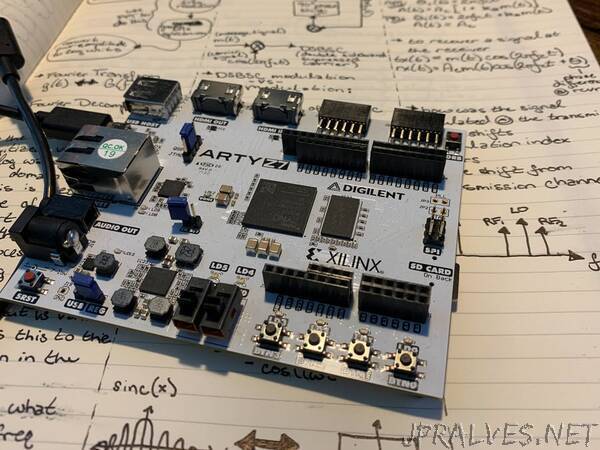

Dsp For Fpga Using Xilinx Dds With Custom Fir Jpralves Net

Comments are closed.