Five Stage Pipelined 32 Bit Risc V Base Integer Instruction Set

Five Stage Pipelined 32 Bit Risc V Base Integer Instruction Set Proprietary technologies with complicated licensing currently dominate the microprocessor industry. as a result, we must seek out a freely available, open sourc. This is a pipelined risc v cpu written in systemverilog; it implements most of the rv32i isa (that is, the rv32i base integer instruction set with no extensions).

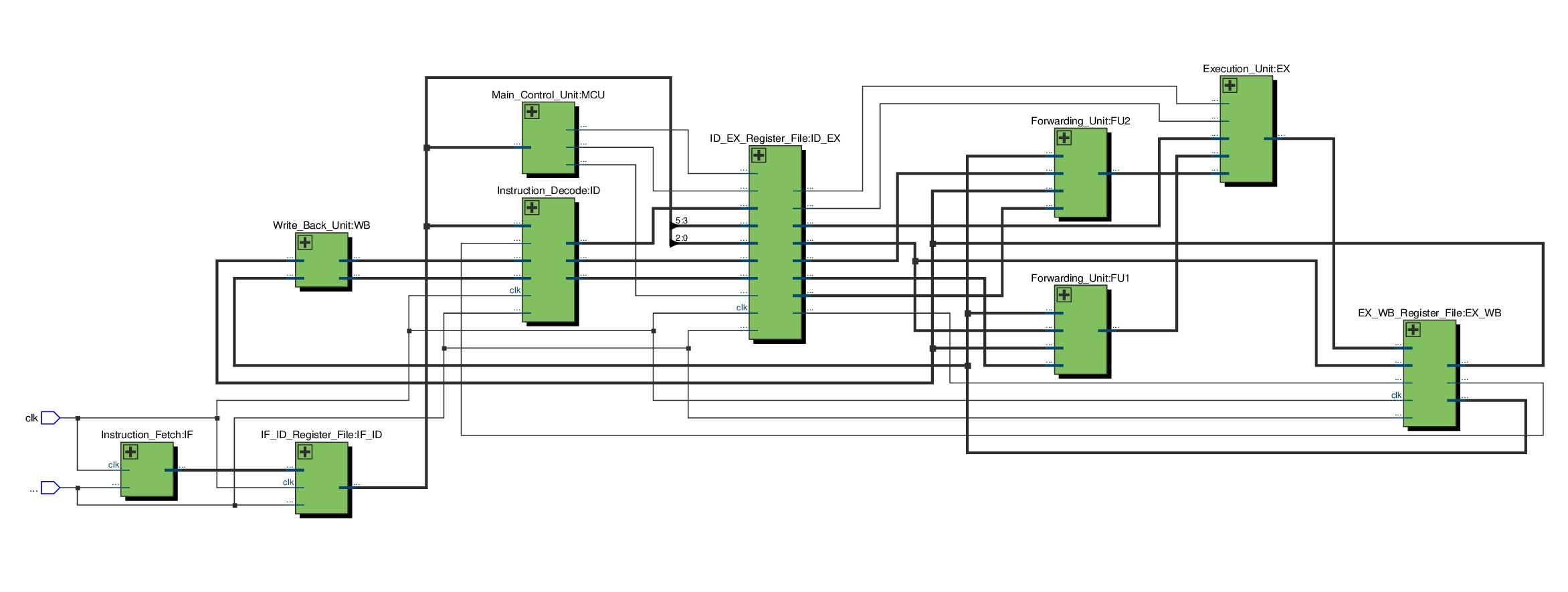

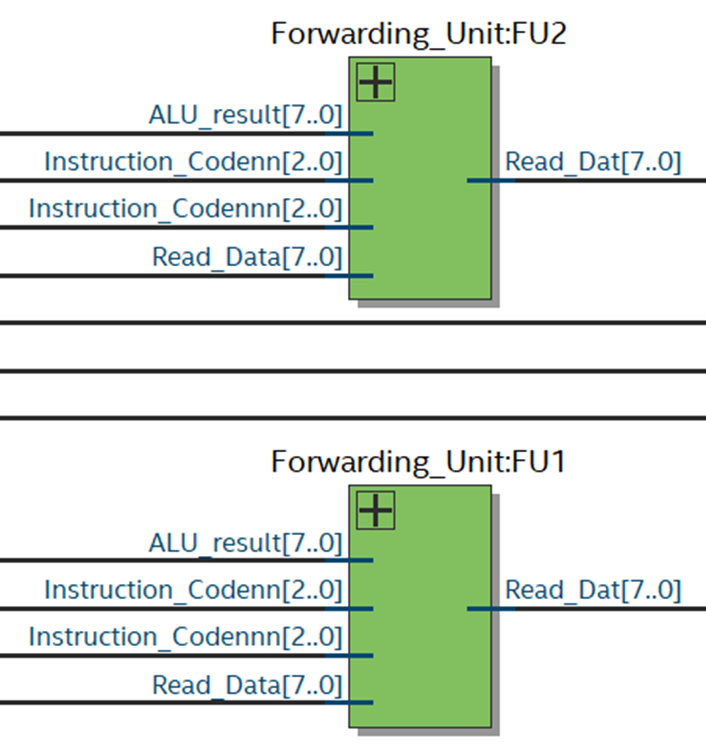

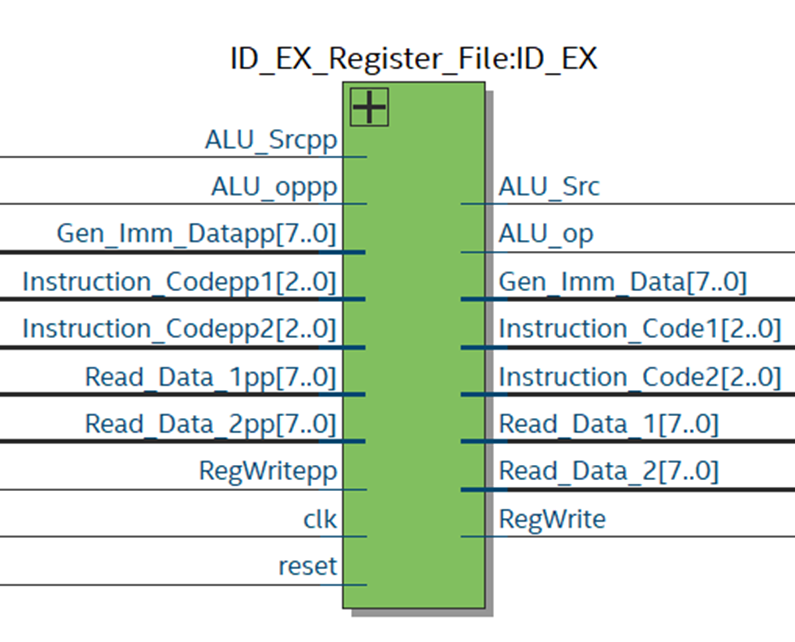

Design Of 32 Bit Risc V Processor With Five Stage Pipeline Instruction In this paper, we discussed the implementation of a five stage pipelined soft processor core. the core uses the risc v rv32i base integer instruction set architecture. In this paper, five stage pipeline risc v processor core rv32i is designed. the papers also discuss hazard removal techniques. the base integer instructions are enough to support operating system environment. instruction fetch, decode, execute, memory, and write back. The document presents the design and fpga implementation of a five stage pipelined risc v processor on a basys 3 fpga board, focusing on the rv32i instruction set architecture. In this paper, the pipeline structure is divided into five stages: fetch, decode, execute, memory and write back. it uses registers to solve the possible hazards of pipelining. the central.

Risc V Pipelined Processor The document presents the design and fpga implementation of a five stage pipelined risc v processor on a basys 3 fpga board, focusing on the rv32i instruction set architecture. In this paper, the pipeline structure is divided into five stages: fetch, decode, execute, memory and write back. it uses registers to solve the possible hazards of pipelining. the central. This document provides a comprehensive technical overview of the riscv pipeline core project, a hardware implementation of a 32 bit risc v processor with a five stage pipelined architecture. The document details the design and implementation of a five stage pipelined risc v processor using verilog, focusing on its architecture and instruction set types. Ul architecture due to its simplicity, flexibility, and cost effectiveness. this paper presents the design and implementation of a 5 stage pipelined risc v processor based on the rv32i instruction set, optimizing processing. This paper discussed the implementation of a five stage pipelined soft processor core that uses the risc v rv32i base integer instruction set architecture and followed the fpga design methodology.

Risc V Pipelined Processor This document provides a comprehensive technical overview of the riscv pipeline core project, a hardware implementation of a 32 bit risc v processor with a five stage pipelined architecture. The document details the design and implementation of a five stage pipelined risc v processor using verilog, focusing on its architecture and instruction set types. Ul architecture due to its simplicity, flexibility, and cost effectiveness. this paper presents the design and implementation of a 5 stage pipelined risc v processor based on the rv32i instruction set, optimizing processing. This paper discussed the implementation of a five stage pipelined soft processor core that uses the risc v rv32i base integer instruction set architecture and followed the fpga design methodology.

Risc V Pipelined Processor Ul architecture due to its simplicity, flexibility, and cost effectiveness. this paper presents the design and implementation of a 5 stage pipelined risc v processor based on the rv32i instruction set, optimizing processing. This paper discussed the implementation of a five stage pipelined soft processor core that uses the risc v rv32i base integer instruction set architecture and followed the fpga design methodology.

Comments are closed.