Design3 8 Decoder Using 2 4 Decoders Siliconvlsi

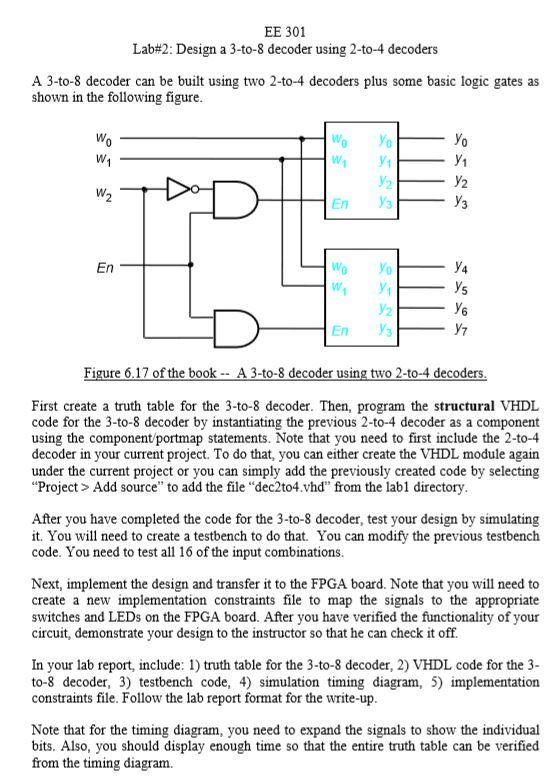

Solved Design 4 To 16 Decoder Using 3 To 8 Decoder Constructed Using 2 Decoders are digital circuits that convert coded inputs into multiple output lines. they play a vital role in various applications where data needs to be decoded and processed. to design the 3:8 decoder we need two 2:4 decoders. why? because we need to have 8 outputs. The 3 x 8 decoder constructed with two 2 x 4 decoders figure shows how decoders with enable inputs can be connected to form a larger decoder. two 2 to 4 line decoders are combined to achieve a 3 to 8 line decoder.

Solved Ee 301 Lab 2 Design A 3 To 8 Decoder Using 2 To 4 Chegg Using only three 2 to 4 decoders with enable and no other additional gates, implement a 3 to 8 decoder with enable. the inputs of the resulting 3 to 8 decoder should be labeled x [2 0] for the code. No description has been added to this video. Explore digital circuits online with circuitverse. with our easy to use simulator interface, you will be building circuits in no time. The problem asks me to make a 3 8 decoder (no enable input required), with inputs x,y,z and 8 active high outputs labelled 0 7. the only building block i can use is a 2 4 decoder with active high enable.

3 To 8 Decoder Using 2 To 4 Decoders Empower Youth Explore digital circuits online with circuitverse. with our easy to use simulator interface, you will be building circuits in no time. The problem asks me to make a 3 8 decoder (no enable input required), with inputs x,y,z and 8 active high outputs labelled 0 7. the only building block i can use is a 2 4 decoder with active high enable. Real world example for practice design a 4 to 16 decoder using two 3 to 8 decoders with an additional control line. Learn how to design and simulate a 3 to 8 decoder using 2 to 4 decoders in verilog with xilinx vivado. this step by step tutorial is perfect for students and fpga enthusiasts, covering. The following figure presents the timing diagram of the 3 to 8 decoder, illustrating the waveforms of the output ports (op0 to op7) as the input lines are selected based on different values of the enable signal (en). Explore digital circuits online with circuitverse. with our easy to use simulator interface, you will be building circuits in no time.

Comments are closed.