Design Mod 12 Synchronous Counter Using Jkff Sequential Logic Circuit Digital Circuit Design

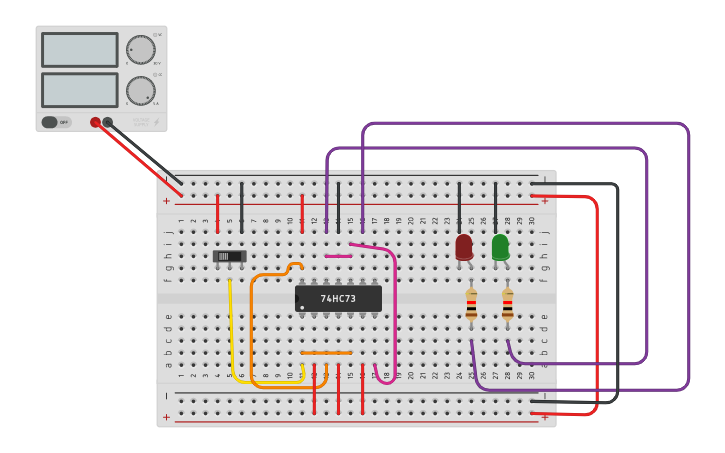

Circuit Design 2 Bit Synchronous Using Jkff Tinkercad This project presents a synchronous modulo 12 counter design using d flip flops in system verilog. an object oriented test bench is used to verify the counter’s functionality, comparing its output against the expected sequence (0000 to 1011). Synchronous mod n counters: here, we have some examples for designing synchronous mod n counters in digital electronics.

Design A Synchronous Sequential Circuit Using Jk Flip Flop Example 5.5.16 design a synchronous up down counter that will count up from zero to one to two to three and will repeat whenever an external input x is logic 0, and will count down from three to two to one to zero and will repeat whenever the external input x is logic 1. The design steps are somewhat similar for both synchronous counter and asynchronous counter but differ slightly. follow the below given steps to design the synchronous counter. Let’s not have an input to trigger each count, but instead let’s act as the clock by substituting a push button switch tied to the positive terminal of our power supply (which is equivalent to a logic 1). Learn the principles and techniques for designing synchronous counters in digital electronics, including types, applications, and design steps.

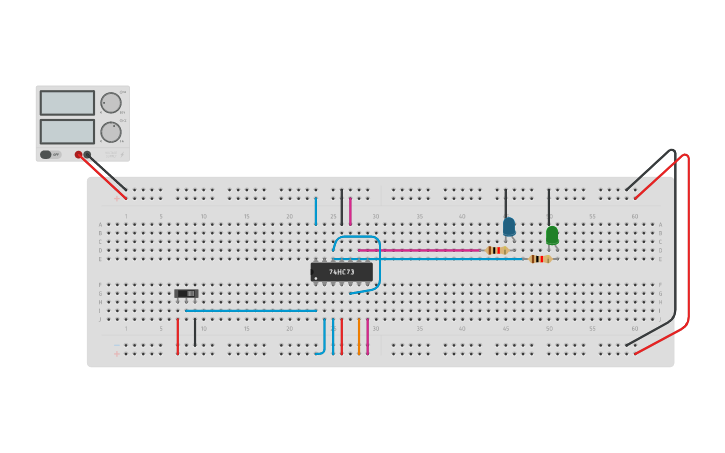

Circuit Design 2 Bit Asynchronous Using Jkff Tinkercad Let’s not have an input to trigger each count, but instead let’s act as the clock by substituting a push button switch tied to the positive terminal of our power supply (which is equivalent to a logic 1). Learn the principles and techniques for designing synchronous counters in digital electronics, including types, applications, and design steps. Since we are designing the sequential circuit using jk and d type flip flops, we need to correlate the required transitions in state transition table with the excitation tables of jk and d type flip flops. This video provides you with a detailed understanding of design mod 12 synchronous counter using jkff. In digital logic and computing, a counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal.

Solved You Want To Design A Synchronous Counter Sequential Chegg Since we are designing the sequential circuit using jk and d type flip flops, we need to correlate the required transitions in state transition table with the excitation tables of jk and d type flip flops. This video provides you with a detailed understanding of design mod 12 synchronous counter using jkff. In digital logic and computing, a counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal.

Comments are closed.