Coding Communication Cpu Microarchitectures As Fast As Possible

Communication Architectures Pdf Parallel Computing Multi Core How do cpus take code electrical signals and translate them to strings of text on screen that a human can actually understand?. To get code to run as fast as possible, developers and compilers — programs that translate programming language into machine readable code — typically use performance models that run the code through a simulation of given chip architectures.

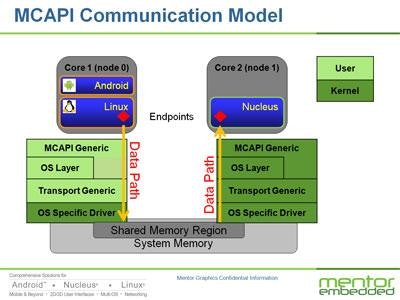

Cpu To Cpu Communications In Multicore Designs Mentor Graphics The present manual describes the details of the microarchitectures of x86 microprocessors from intel, amd, and via. the itanium processor is not covered. the purpose of this manual is to enable assembly programmers and compiler makers to optimize software for these microprocessors. We discussed what a cpu was, a brief history of the cpu, we explained the concept of computing abstraction layers, and instruction set architectures. the isa is what we normally refer to as. This lecture is intended for an advanced course on computer architecture, suitable for gradu ate students or senior undergrads who want to specialize in the area of computer architecture. it is also intended for practitioners in the industry in the area of microprocessor design. I recently gave a talk at qcon london entitled “understanding cpu microarchitecture for performance” on the details of cpu internals and how they affect the speed of programs that run on them.

Processor Communication Architecture Download Scientific Diagram This lecture is intended for an advanced course on computer architecture, suitable for gradu ate students or senior undergrads who want to specialize in the area of computer architecture. it is also intended for practitioners in the industry in the area of microprocessor design. I recently gave a talk at qcon london entitled “understanding cpu microarchitecture for performance” on the details of cpu internals and how they affect the speed of programs that run on them. This would allow up to four instructions to be "in flight" at one time, making the processor look four times as fast. although any one instruction takes just as long to complete (there are still four steps) the cpu as a whole "retires" instructions much faster. The performance of a cpu is not solely determined by its clock speed or the number of cores it has; the underlying microarchitecture plays a crucial role. this article delves into the intricacies of cpu microarchitecture and explores how it impacts overall performance. Cycle level simulators such as gem5 are widely used in microarchitecture design, but they are prohibitively slow for large scale design space explorations. we present concorde, a new methodology for learning fast and accurate performance models of microarchitectures. Unlike in the early days of risc architec tures it is possible, at least to some degree, to develop new communication architectures without developing new hardware.

Comments are closed.