1 Upload The Code Of 3×8 Decoder And Its Testbench Chegg

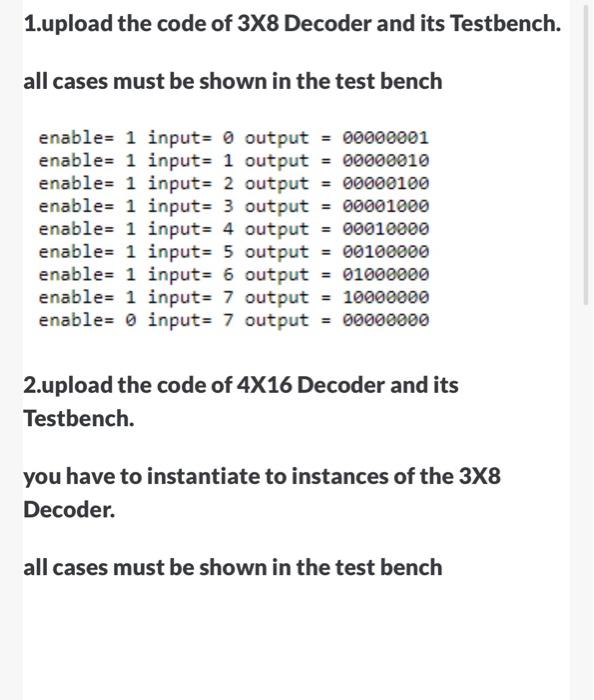

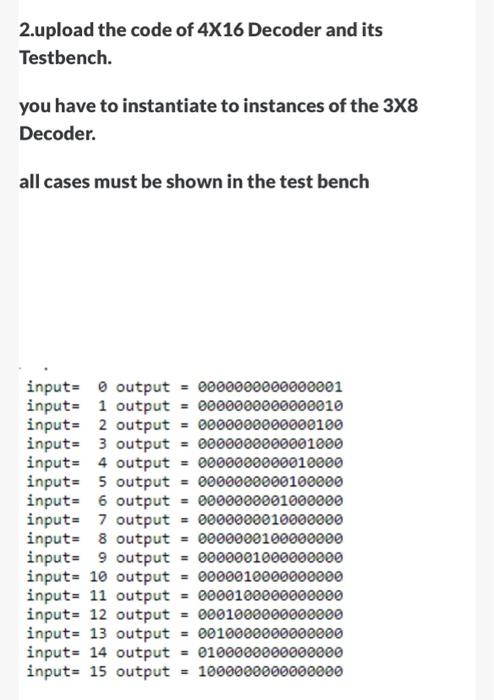

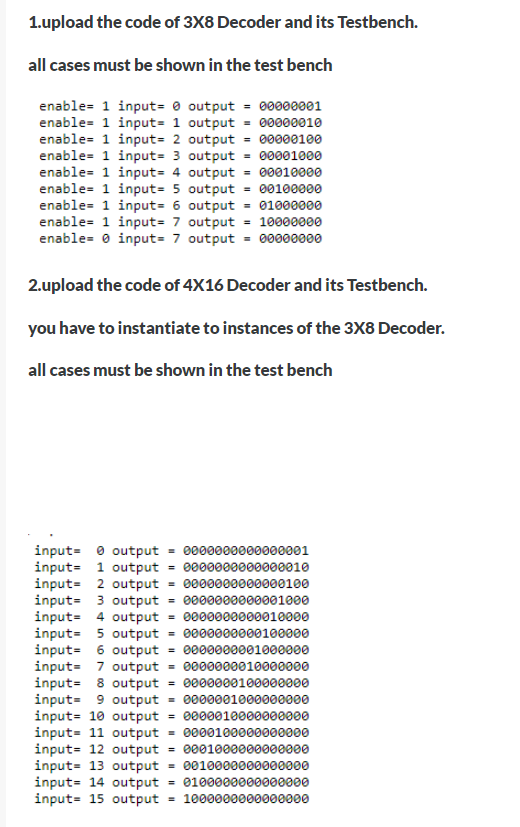

Solved 2 Upload The Code Of 4x16 Decoder And Its Testbench Chegg Question: 1.upload the code of 3x8 decoder and its testbench. all cases must be shown in the test bench = enable= 1 input= output = 00000001 enable= 1 input= 1 output = 00000010 enable= 1 input= 2 output = 00000100 enable= 1 input= 3 output = 00001000 enable= 1 input= 4 output = 00010000 enable= 1 input= 5 output = 00100000 enable= 1 input= 6. A brief description of decoder circuits .how to write the verilog code of 3x8 decoder circuit in structural modeling style.verification of verilog code of 3x8 decoder using testbench.

Solved 1 Upload The Code Of 3x8 Decoder And Its Testbench Chegg Write a verilog hdl module to describe the 3x8 decoder shown below and write a testbench that will consider all possible combinations of inputs. (simulation is not required). Complete uvm testbench for verification of 3x8 decoder uvm testbench for 3x8 decoder readme.md at main · vivek dave uvm testbench for 3x8 decoder. Objective: the main objective of this program is to learn how to use case statement writing test bench and verify the functionality of 3x8 decoder and must simulate, synthesize and view rtl schematics for the same. This document provides instructions for designing and simulating a 3x8 decoder using both structural and behavioral verilog modules. the structural design is to be created using and, or, and inv gates without always statements, while the behavioral design uses a single always block.

Solved 1 Upload The Code Of 3x8 Decoder And Its Testbench Chegg Objective: the main objective of this program is to learn how to use case statement writing test bench and verify the functionality of 3x8 decoder and must simulate, synthesize and view rtl schematics for the same. This document provides instructions for designing and simulating a 3x8 decoder using both structural and behavioral verilog modules. the structural design is to be created using and, or, and inv gates without always statements, while the behavioral design uses a single always block. Question: please write a verilog code that satisfied the testbench this is the intro of the code module decoder3x8 (in,out,enable); input [2:0]in; input enable; output. This verilog code implements a 3x8 decoder using two 2x4 decoders at the gate level. we'll assume active low outputs for the 2x4 decoders for clarity, and the final 3x8 decoder will also have active low outputs. Complete uvm testbench for verification of 3x8 decoder vivek dave uvm testbench for 3x8 decoder. Lab 2 introduction: in this lab, we will be building a 3 to 8 decoder by using two 2 to 4 decoders plus some logic gates. we will be creating a truth table and then create the vhdl module.

1 Upload The Code Of 3x8 Decoder And Its Testbench Chegg Question: please write a verilog code that satisfied the testbench this is the intro of the code module decoder3x8 (in,out,enable); input [2:0]in; input enable; output. This verilog code implements a 3x8 decoder using two 2x4 decoders at the gate level. we'll assume active low outputs for the 2x4 decoders for clarity, and the final 3x8 decoder will also have active low outputs. Complete uvm testbench for verification of 3x8 decoder vivek dave uvm testbench for 3x8 decoder. Lab 2 introduction: in this lab, we will be building a 3 to 8 decoder by using two 2 to 4 decoders plus some logic gates. we will be creating a truth table and then create the vhdl module.

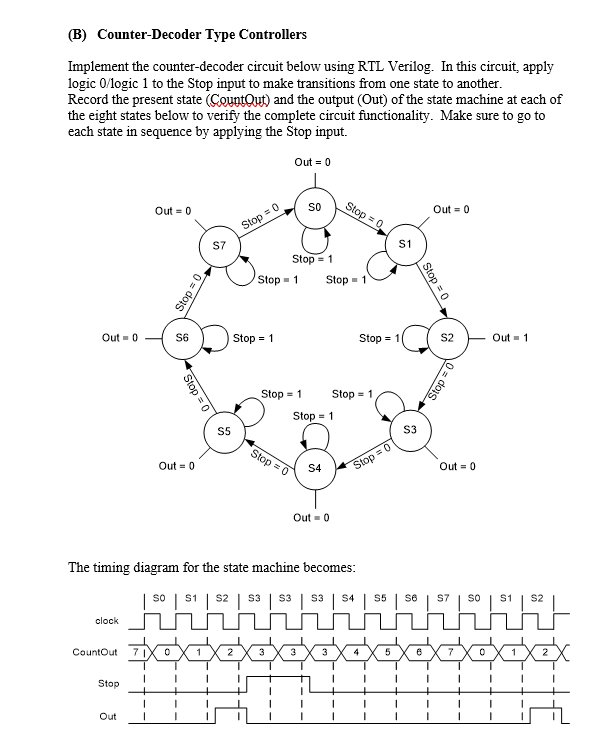

Solved Provide The Module Code And The Testbench Code Or I Chegg Complete uvm testbench for verification of 3x8 decoder vivek dave uvm testbench for 3x8 decoder. Lab 2 introduction: in this lab, we will be building a 3 to 8 decoder by using two 2 to 4 decoders plus some logic gates. we will be creating a truth table and then create the vhdl module.

Comments are closed.